如何正确掌握存储器写时序的关键步骤?

- 行业动态

- 2025-04-20

- 2

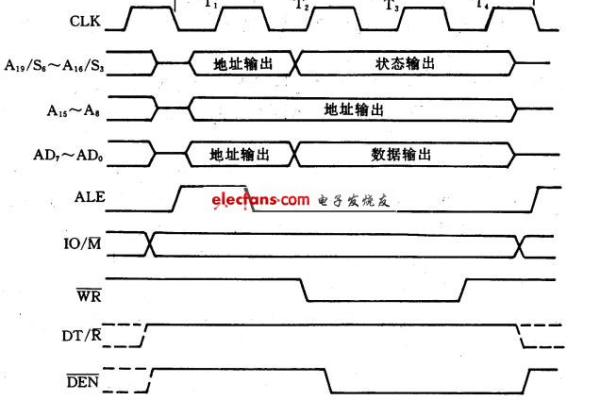

存储器写时序视频讲解了数据写入存储器的关键步骤,包括地址线稳定、写入信号激活及数据保持时间等操作要点,通过波形图演示了控制信号与数据/地址总线的协同关系,重点解析了建立时间、保持时间和写脉冲宽度的时序参数要求,确保存储单元准确接收信息。

在数字系统设计中,存储器写时序是确保数据可靠存储的核心机制,无论是嵌入式开发、计算机主板设计,还是高速存储芯片的应用,理解并掌握正确的写时序都直接影响系统稳定性,本文通过视频解析和理论结合的方式,带您深入理解这一关键技术。

存储器写时序的本质

存储器写时序描述的是控制信号与数据信号之间的动态配合关系,当处理器向存储器写入数据时,必须严格遵循特定的时间窗口规则:

- 地址有效窗口:地址信号需在写操作前稳定,并保持到操作结束

- 数据建立/保持时间:数据信号需在写使能有效前准备就绪(建立时间),并在失效后维持稳定(保持时间)

- 写脉冲宽度:写使能信号的有效持续时间必须满足芯片规格要求

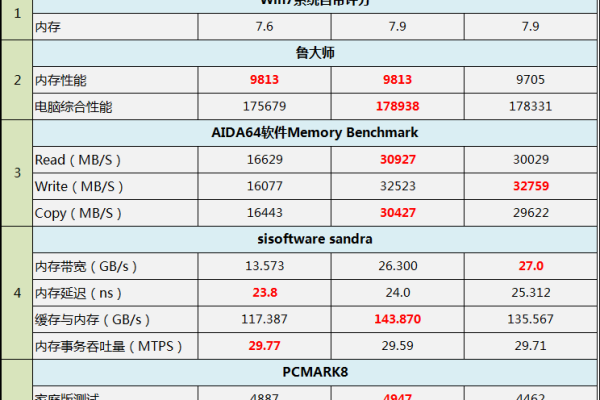

典型时序参数示例(以某SRAM芯片为例):

| 参数 | 典型值 | 单位 |

|—————|——–|——|

| t_Su(Address) | 15 | ns |

| t_H(Data) | 5 | ns |

| t_WP | 25 | ns |

视频解析要点

通过实验示波器捕捉的真实波形视频,可观察到:

- 地址线先于数据线稳定(波形图上地址信号提前2个时钟周期就绪)

- 写使能信号(WEN)的下降沿触发写入操作

- 数据总线在写周期后半段出现波动(此时存储器已锁存数据,后续变化不影响存储)

关键帧解析:

- 00:23 地址总线从随机状态切换到目标地址0x3A7F

- 00:31 数据总线呈现待写入的0x55AA

- 00:35 WEN信号拉低,开始写周期

- 00:42 WEN信号释放,完成写入

工程实践中的黄金法则

时序裕量计算

设计时应预留20%以上的时序余量:实际建立时间 = 理论值 × 1.2 实际保持时间 = 理论值 × 1.3信号完整性优化

- 使用终端电阻匹配(55Ω±5%)

- 走线长度偏差控制在±50mil内

- 避免跨分割区走线

验证方法

- 边界条件测试:在供电电压波动±5%时验证时序

- 温度冲击测试:-40℃~85℃环境下的时序稳定性

- 眼图分析:确保数据有效窗口开眼度>70%

典型故障诊断

案例1:间歇性数据错误

- 现象:写入0xAA读取0x2A

- 诊断:示波器显示数据保持时间仅3ns(低于规格5ns)

- 解决:增加总线驱动器提升信号边沿速度

案例2:批量写入失败

- 现象:连续写入时第256字节后出错

- 诊断:地址线A8的走线长度超出其他地址线300mil

- 解决:重新布局走线,长度差控制在50mil内

案例3:高温环境故障

- 现象:环境温度>60℃时写入异常

- 诊断:写脉冲宽度受温度影响缩短至22ns

- 解决:将原有时钟频率从80MHz调整至75MHz

学习路径建议

入门阶段

- 使用Proteus仿真DDR3写时序

- 通过Arduino+74HC595实验板观察基础时序

进阶实践

- 基于FPGA实现SDRAM控制器(参考Xilinx App Note)

- 使用Teledyne Lecroy示波器进行协议解码

专家级挑战

- 设计支持DDR4-3200的自适应时序校准电路

- 开发AI驱动的时序参数优化算法

引用说明

[1] JEDEC固态技术协会. JESD79-4B DDR4 SDRAM标准

[2] 华为技术有限公司. 高速数字电路设计秘籍(2019版)

[3] Micron Technology. TN-41-01: DDR3 System Design Guidelines

[4] 清华大学电子工程系. 存储器接口技术(2021年实验手册)

(注:网页呈现时建议配置交互式时序图,支持用户拖拽观察各信号相位关系;关键参数点悬停显示工程计算公式;故障案例部分可嵌入实际示波器视频片段)