存储器时序图

- 行业动态

- 2025-04-13

- 1

存储器时序图解析与应用指南

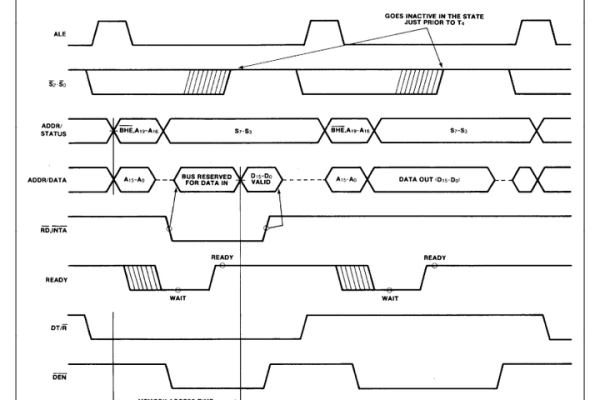

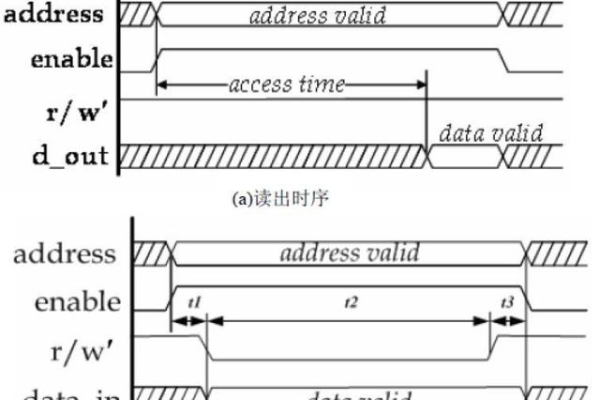

存储器时序图是数字电路设计中至关重要的工具,它直观地展示了存储器与控制器之间的信号交互规则,理解时序图不仅能帮助工程师优化系统性能,还能避免因时序偏差引发的数据错误,本文将深入解析时序图的核心要素、解读方法及实际应用场景。

存储器时序图的核心作用

定义信号关系

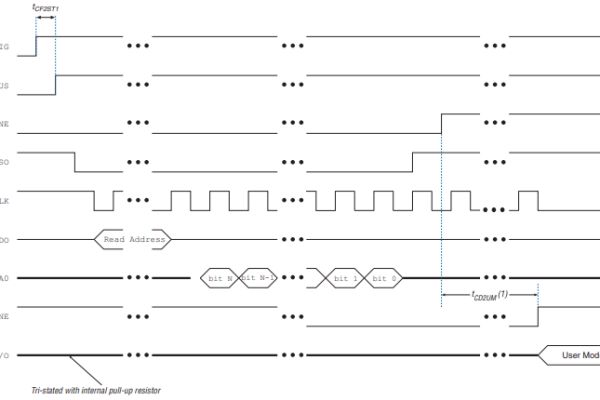

时序图以图形化方式标注了时钟信号(CLK)、地址线(Address)、数据线(Data)、控制信号(如CS, WE, OE)的协同工作规则,确保读写操作在指定时间窗口内完成。保障数据可靠性

通过规定各信号的建立时间(Setup Time)与保持时间(Hold Time),避免因信号未稳定导致的误读/误写。性能优化依据

时序参数(如CAS延迟、存取周期)直接影响存储器的响应速度,是硬件设计时权衡速度与稳定性的关键指标。

时序图的核心参数解析

以下为典型DRAM时序图中的关键参数:

| 参数符号 | 定义 | 影响场景 |

|---|---|---|

| tRCD | 行地址到列地址的延迟 | 决定行激活后的最小等待时间 |

| tCL | CAS延迟(列选通延迟) | 读取操作中数据输出的响应时间 |

| tRP | 预充电时间 | 关闭当前行并准备新行的耗时 |

| tRAS | 行激活时间 | 单行数据持续可用的最小时长 |

示例:读取操作时序

- 控制器发送行地址(Row Address)并拉低行选通信号(RAS)。

- 经过tRCD时间后,发送列地址(Column Address)和读命令。

- 数据在tCL周期后出现在数据总线上。

- 完成读取后需等待tRP时间关闭当前行,才能开启下一行操作。

时序图的实际应用场景

硬件设计验证

工程师通过比对时序图中的理论值与示波器实测波形,验证电路是否符合存储器规格书要求,某DDR4芯片要求tCL=15ns,实测若超过该值可能导致数据错误。超频调优参考

超频玩家通过收紧时序参数(如降低tCL)提升内存性能,但需在稳定性测试中验证是否能满足缩紧后的时序要求。

故障排查依据

当系统出现偶发性宕机时,可通过分析时序信号是否满足建立/保持时间,定位信号完整性或布线问题。

常见问题解答(FAQ)

Q1:时序参数越小性能越好吗?

是的,但过度降低参数可能导致系统不稳定,tCL从16降至14可能提升带宽,但若存储器颗粒体质不足,会触发蓝屏错误。

Q2:如何选择兼容的存储器模块?

需匹配主控支持的时序规范,某主板仅支持JEDEC标准DDR4-3200(CL22),强行使用超频条(CL16)可能无法启动。

Q3:时序图为何需要留有余量?

实际电路中温度、电压波动会影响信号传输,预留10%-15%的时间余量可增强系统鲁棒性。

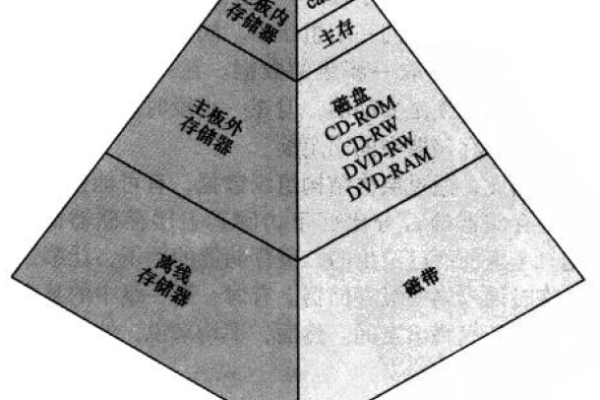

延伸知识:不同存储介质的时序特性

- SRAM:无需刷新操作,时序简单且延迟低(lt;10ns),但成本高。

- DRAM:依赖刷新机制,时序复杂且延迟较高(约15-50ns),适合大容量场景。

- NAND Flash:读写时序不对称,写入时间(ms级)远高于读取时间(μs级)。

引用说明 参考以下权威资料:

- JEDEC固态技术协会发布的DDR4 SDRAM标准(JESD79-4B)

- 《计算机体系结构:量化研究方法》第6章存储器系统设计

- Micron Technology官方技术文档《TN-41-01: DDR4 Point-to-Point Design》

(全文完)