存储器的地址译码方式

- 行业动态

- 2025-04-12

- 2

存储器的地址译码方式分为线选法和重合法两种,线选法通过单级译码器直接选址,结构简单但地址线利用率低;重合法采用行列双译码结构,通过交叉定位减少地址线数量,适合大容量存储器,提高了空间效率但电路复杂度较高,两种方式根据存储容量和性能需求选择应用。

在计算机系统中,存储器地址译码是实现数据存取的核心机制之一,它决定了如何将CPU发送的地址信号转换为对应存储单元的物理位置,常见的地址译码方式包括线选法、部分译码和全译码,每种方式都有其独特的实现逻辑与应用场景。

地址译码的基本原理

存储器由多个存储单元构成,每个单元有唯一地址,CPU通过地址总线发送二进制地址信号,译码电路将其转换为对应的控制信号,选中目标单元,译码过程类似于“地图坐标定位”,需满足以下要求:

- 唯一性:每个地址对应唯一存储单元

- 高效性:译码延迟需尽可能小

- 扩展性:支持存储器容量扩展

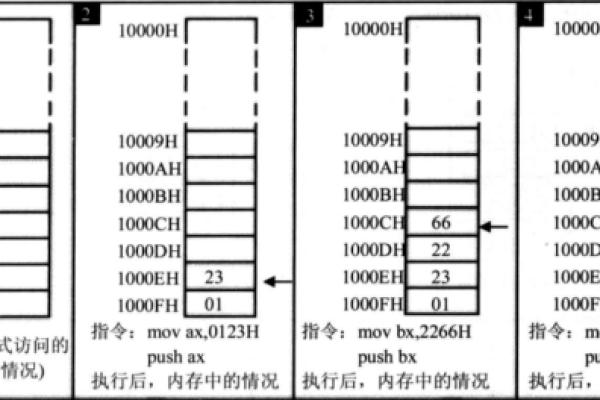

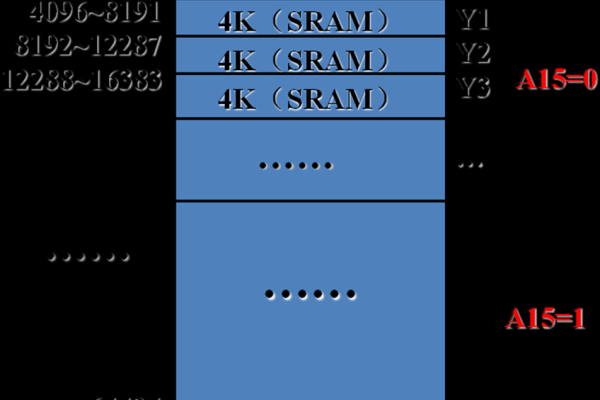

线选法(Linear Selection)

实现方式

直接将地址总线的高位作为片选信号,低位用于寻址芯片内部单元。

- 地址总线:A15~A0(16位)

- 使用A15作为片选信号时:

- A15=0:选中低32KB存储空间(0000H~7FFFH)

- A15=1:选中高32KB存储空间(8000H~FFFFH)

特点

优点:

- 电路简单,成本低

- 无需复杂译码器

缺点:

- 地址空间不连续,存在”地址空洞”

- 扩展性差,易造成资源浪费

- 可能出现多个存储芯片同时被选中的冲突

典型应用:早期单片机系统、小容量嵌入式设备

部分译码(Partial Decoding)

实现方式

仅对部分地址位进行译码,未参与的地址位状态不影响选通。

- 使用A15和A14进行译码:

- A15=0, A14=0 → 选中芯片1

- A15=0, A14=1 → 选中芯片2

- (其他组合不译码)

特点

优点:

- 比线选法更灵活

- 可减少译码器使用数量

缺点:

- 存在地址重叠现象(未译码位可为0或1)

- 存储空间利用率仍不理想

典型应用:中等规模系统,对成本敏感的场景

全译码(Full Decoding)

实现方式

对所有地址位进行完全译码,典型方案包括:

- 3-8译码器(74LS138):用3位输入生成8个片选信号

- 4-16译码器:扩展更大存储空间

- 级联译码:多级译码器组合实现深度扩展

特点

优点:

- 地址空间无重叠,利用率100%

- 支持大容量存储扩展

- 系统稳定性高

缺点:

- 需要额外译码芯片

- 电路复杂度增加

- 时序控制要求更高

典型应用:现代计算机、服务器等大规模存储系统

三种方式的对比分析

| 对比维度 | 线选法 | 部分译码 | 全译码 |

|---|---|---|---|

| 电路复杂度 | |||

| 地址空间利用率 | ≤50% | 50%~80% | 100% |

| 扩展能力 | 单芯片 | 有限扩展 | 无限制扩展 |

| 成本 | 最低 | 中等 | 较高 |

| 可靠性 | 易冲突 | 可能重叠 | 无冲突 |

技术选型建议

- 简单控制系统:优先考虑线选法

- 中等规模系统:采用部分译码+地址隔离

- 高性能系统:必须使用全译码方案

- 特殊需求场景:

- 需快速响应的实时系统:可结合线选法与缓存技术

- 超大规模存储:采用Bank切换+分级译码

技术发展趋势

- 动态地址重映射:通过FPGA实现可编程译码逻辑

- 智能预译码:结合机器学习预测访问模式

- 光子译码技术:利用光信号提升译码速度(实验室阶段)

- 量子地址译码:基于量子叠加态的并行译码(理论探索)

引用说明

本文技术原理参考《计算机组成与设计》(David Patterson著)、IEEE存储技术标准(IEEE 1003.1)及JEDEC固态存储器规范(JESD220C),实际电路案例基于74系列芯片数据手册分析。