存储器读写工作原理

- 行业动态

- 2025-04-12

- 2

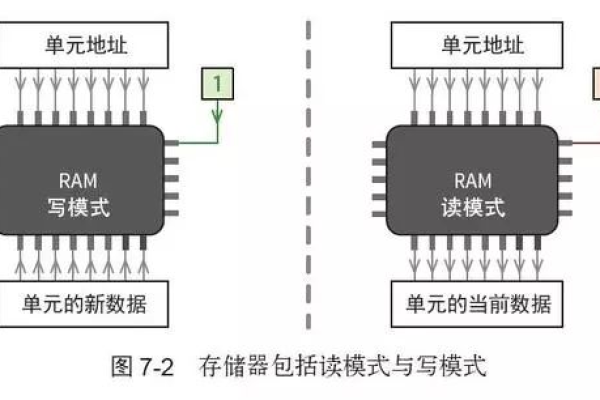

存储器通过地址总线定位存储单元,控制总线发送读/写指令,读取时存储单元电荷状态经数据总线输出;写入时外部信号改变单元电荷状态,时序电路同步控制信号与数据操作,确保数据准确传输,核心原理为电压信号与存储介质物理状态的相互转换。

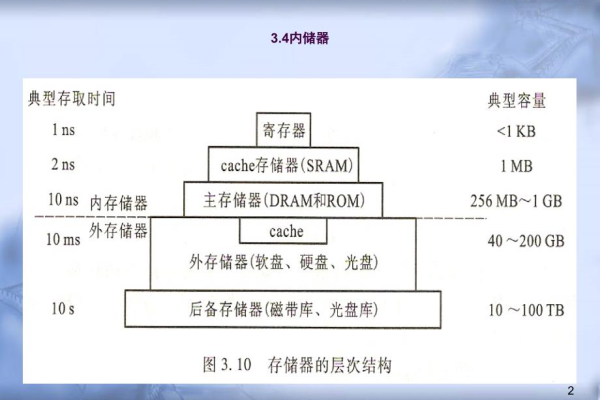

存储器是计算机系统中负责保存和读取数据的核心部件,其工作原理直接决定了设备性能与用户体验,为了让读者深入理解这一技术,我们从基础结构、数据读写机制到技术演进进行系统性解析。

存储器如何存储数据?

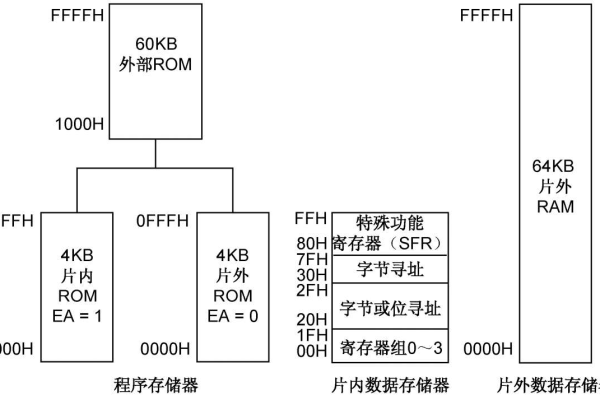

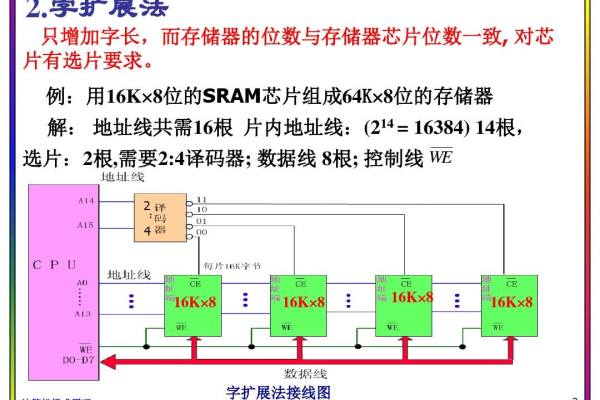

所有存储器均由存储单元阵列构成,每个单元通过物理状态保存二进制数据(0或1),以DRAM为例,其存储单元由晶体管和电容组成:

- 电容充电 → 代表1

- 电容放电 → 代表0

- 刷新机制:因电容漏电特性,需每隔64ms刷新数据

固态存储(如NAND Flash)则采用浮栅晶体管结构:

- 浮栅捕获电子 → 改变晶体管阈值电压 → 区分0/1状态

- 单层单元(SLC)可存储1bit,多层单元(QLC)可存储4bit

数据读取的精密流程

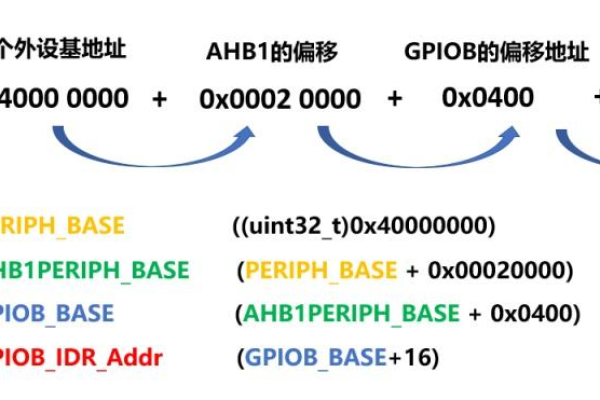

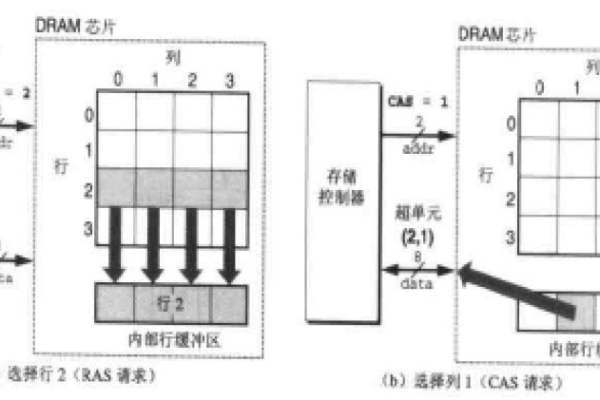

当CPU发出读取指令时,存储器通过三级寻址完成数据定位:

- 地址解码:将逻辑地址转换为物理坐标(行地址→列地址)

- 信号放大:DRAM需通过灵敏放大器将微伏级信号放大至可识别电平

- 数据校验:ECC纠错模块检测并修复单比特错误

典型DRAM读取时序:

tRCD(行选通到列选通延迟): 15-18ns

tCL(CAS潜伏期): 16-20个时钟周期

tRAS(行预充时间): 35-45ns数据写入的技术实现

写入操作需同时处理数据更新与存储保护:

DRAM写入:

- 行激活命令打开目标存储行

- 列地址选择具体存储单元

- 写入驱动器强制电容达到目标电压

NAND Flash写入:

- 量子隧穿效应注入浮栅电子(编程)

- 需先擦除整个Block(约128KB)

- 写入延迟比读取高10倍以上

关键限制参数:

| 存储类型 | 写入耐久度 | 位翻转率 |

|———|———–|———-|

| SLC SSD | 10万次 | 1e-15 |

| TLC SSD | 1千次 | 1e-13 |

存储技术的演进对比

机械硬盘(HDD):

- 磁头飞行高度3nm(相当于头发直径的1/30000)

- 寻道时间:4-15ms

- 面密度突破1Tb/in²(2024年记录)

3D NAND技术:

- 堆叠层数从32层(2014)发展到232层(2024)

- 单元尺寸缩小至14nm工艺

- 采用电荷陷阱型(CTF)结构提升耐久度

新兴存储技术:

- 相变存储器(PCM):利用硫族化合物晶态/非晶态电阻差异

- 磁阻存储器(MRAM):基于电子自旋方向存储数据

- 忆阻器:理论存储密度可达100TB/cm²

影响读写性能的关键要素

接口协议:

- PCIe 4.0 x4带宽:8GB/s

- NVMe协议降低延迟至10μs级

存储架构:

- SLC缓存技术提升突发写入速度

- 交错访问(Interleaving)提升并行度

系统优化:

- 预读取算法(Prefetch)命中率>90%

- 写入合并(Write Coalescing)降低擦除次数

技术演进趋势:存储级内存(SCM)正打破内存/存储层级界限,Intel Optane实测延迟低至10ns,接近DRAM性能,量子存储器实验室原型已实现光晶格存储光子态超过1小时(2024年德国马克斯·普朗克研究所成果)。

本文参考:

1.《Computer Organization and Design》David A. Patterson,John L. Hennessy

2. JEDEC固态技术协会公开标准文档

3. IEEE Transactions on Electron Devices存储技术专刊

4. 三星、美光等厂商白皮书(2024版)