存储器 字线 时钟

- 行业动态

- 2025-04-11

- 2

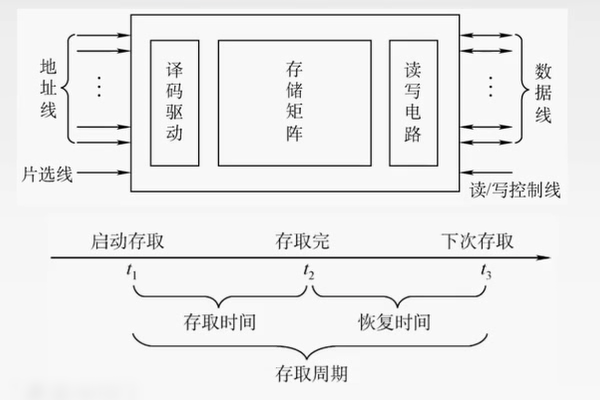

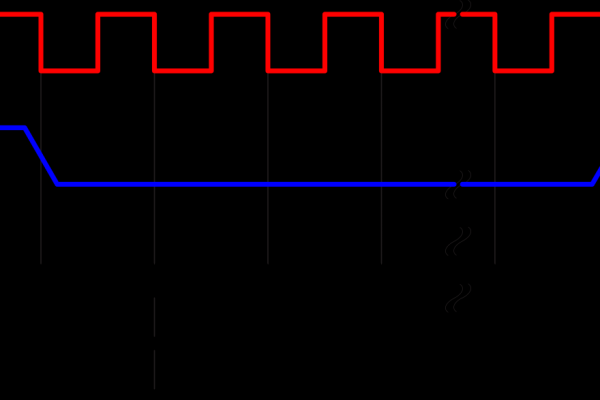

存储器通过字线选择特定存储单元进行读写操作, 字线由地址译码器驱动并与存储阵列的行对应,时钟信号同步控制 存储器操作时序,协调地址、数据与读写信号的变化,确保信息在稳定周期内完成存取,避免时序冲突,提升存储系统的可靠性和效率。

存储器:数据存储的基石

存储器是电子系统中用于存储程序、数据及临时运算结果的核心部件,主要分为易失性存储器(如RAM)和非易失性存储器(如ROM、闪存)两类,其核心结构由存储单元阵列组成,每个存储单元可保存1位(bit)或更多数据。

存储单元的工作原理

存储单元通过晶体管和电容(如DRAM)或浮栅晶体管(如闪存)实现数据保存,以DRAM为例:- 写入数据:通过字线激活目标单元,位线(Bit Line)施加电压,改变电容电荷状态。

- 读取数据:字线激活后,电容电荷变化被位线检测并放大,输出为逻辑0或1。

存储器的分类与性能指标

- RAM(随机存取存储器):支持高速读写,但断电后数据丢失。

- ROM(只读存储器):数据永久存储,用于固件等场景。

- 关键指标:容量、读写速度(纳秒级延迟)、功耗。

字线(Word Line):存储单元的“地址标签”

字线是存储器中用于选择特定存储单元的控制线,通常与位线(Bit Line)正交排布,形成存储阵列的地址网格。

字线的核心功能

- 地址解码:接收来自地址总线的信号,通过行地址解码器选中特定行。

- 激活存储单元:选中行的字线电压升高,使该行所有存储单元与位线连通。

字线与存储密度的关系

字线数量直接决定存储器的行数,一个1024行的存储器需要10位地址线(2¹⁰=1024),现代高密度存储器(如3D NAND)通过垂直堆叠字线提升容量。

时钟信号:同步操作的指挥棒

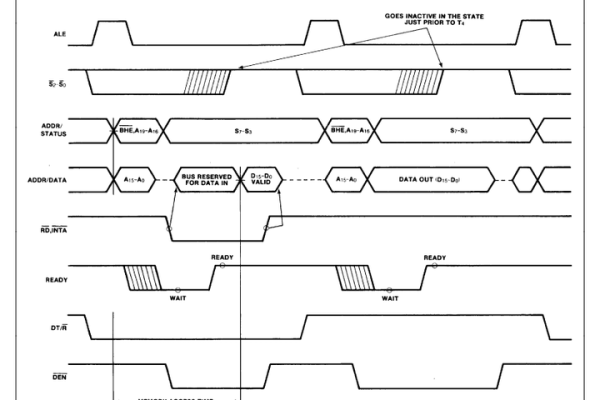

时钟信号是数字电路中的周期性脉冲,用于协调存储器与其他组件(如CPU、总线)的时序操作。

时钟频率与存储器性能

- 同步DRAM(SDRAM):读写操作与时钟上升沿同步,时钟频率越高,带宽越大(如DDR5频率可达6400 MHz)。

- 时序参数:包括tRCD(行地址到列地址延迟)、tCL(CAS延迟)等,需与时钟周期匹配以避免数据错误。

时钟抖动与稳定性

时钟信号的相位噪声或抖动可能导致时序偏差,高精度时钟发生器(如PLL)用于稳定信号,保障存储器的可靠读写。

三者的协同工作机制

以一次存储器读写操作为例:

- 地址输入:CPU通过地址总线发送目标地址。

- 字线激活:行地址解码器选中对应字线,激活整行存储单元。

- 时钟同步:时钟信号触发列地址解码器与读写电路,通过位线完成数据传输。

- 数据输出/写入:读取时,数据经放大后通过总线传回CPU;写入时,数据由总线写入存储单元。

常见问题解答

- 字线与位线有何区别?

字线负责选择行,位线负责传输列数据,二者共同定位存储单元。 - 时钟频率是否越高越好?

高频提升带宽,但也可能因时序限制导致稳定性问题,需平衡性能与可靠性。 - 存储器的寿命如何评估?

非易失性存储器(如SSD)依据写入次数(P/E周期)评估寿命,易失性存储器(如DRAM)寿命通常由电路老化决定。

引用说明参考以下权威资料:

- 《Computer Organization and Design》(David A. Patterson, John L. Hennessy)

- IEEE论文《3D NAND Flash Memory: Technology and Challenges》

- 三星电子《DRAM技术手册》