如何在Shopify上成功注册并开设我的在线商店?

- 行业动态

- 2024-10-03

- 3014

Shopify开店注册教程(详细流程)

Shopify是一个流行的电子商务平台,它允许商家轻松创建和管理在线商店,无论你是新手还是有经验的卖家,Shopify都提供了一套完整的工具来帮助你启动和运营你的在线业务,以下是详细的Shopify开店注册流程:

1. 准备工作

在开始之前,请确保你有以下几项准备:

一个有效的电子邮件地址

一个支付方式(如信用卡或PayPal账户),用于支付Shopify的月费

你的个人信息,包括姓名、地址、电话号码等

你的商店名称和品牌标识(如Logo)

2. 访问Shopify官网并注册

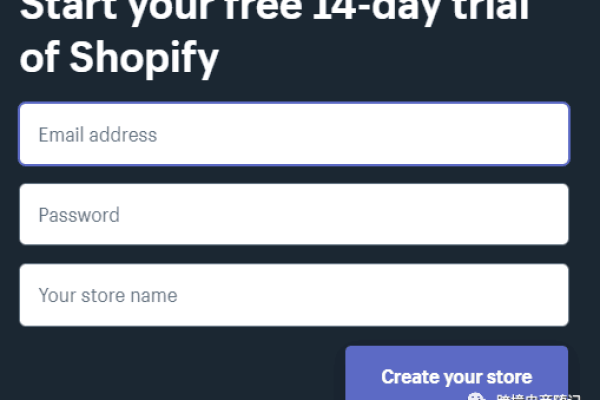

前往 [Shopify官网](https://www.shopify.com/),点击页面上的“Start free trial”按钮开始免费试用,你需要填写一些基本信息,包括:

| 字段 | 描述 |

| 你的电子邮箱地址 | |

| Password | 你的密码 |

| Your store name | 你商店的名称 |

| Store address | 你商店的地址 |

| Store currency | 你商店的货币单位 |

| Account type | 选择个人账户或个人+账户 |

填写完毕后,点击“Create your store”按钮。

3. 设置商店信息

注册后,你会进入Shopify的管理面板,你需要设置一些基本的商店信息:

3.1 添加产品

点击左侧菜单中的“Products”选项卡。

点击“Add product”按钮添加新产品。

填写产品标题、描述、价格等信息。

上传产品图片。

保存产品信息。

3.2 设置支付方式

在左侧菜单中选择“Settings”。

点击“Payments”选项卡。

根据需要设置支付网关,如PayPal、Stripe等。

3.3 配置运费

在“Settings”菜单下选择“Shipping”。

设置你的运费规则。

3.4 定制主题

在左侧菜单中选择“Online store”。

点击“Themes”选项卡。

浏览可用的主题,选择一个你喜欢的并安装。

自定义主题的颜色、字体和布局以匹配你的品牌形象。

3.5 添加域名

在“Online store”菜单下选择“Domains”。

如果你已经有了自己的域名,可以将其连接到Shopify。

如果没有,可以在Shopify购买一个新的域名。

4. 发布你的商店

完成以上设置后,你可以预览你的商店,确保一切看起来都不错,如果满意,点击“Publish”按钮发布你的商店。

5. 管理和维护

一旦你的商店上线,你需要定期管理和维护它,包括更新产品信息、处理订单、回应客户咨询等。

相关问题与解答

Q1: Shopify的费用是多少?

A1: Shopify提供不同的定价计划,包括Lite、Basic、Pro和Unlimited,费用从每月9美元到299美元不等,具体取决于你选择的计划和服务需求,还可能需要支付额外的交易费用和第三方应用费用。

Q2: 我可以在Shopify上销售数字产品吗?

A2: 是的,你可以在Shopify上销售数字产品,如电子书、音乐、软件等,在添加产品时,只需选择产品类型为“Digital”,然后上传你的数字文件即可,客户购买后,系统会自动发送下载链接给他们。

以上就是关于“Shopify开店注册教程(详细流程)”的问题,朋友们可以点击主页了解更多内容,希望可以够帮助大家!

本站发布或转载的文章及图片均来自网络,其原创性以及文中表达的观点和判断不代表本站,有问题联系侵删!

本文链接:https://www.xixizhuji.com/fuzhu/7444.html