负载均衡在Web应用中的应用场景

- 行业动态

- 2024-07-12

- 1

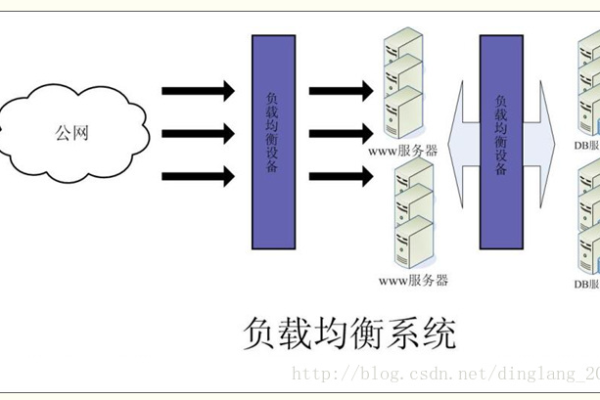

负载均衡技术在Web应用中的应用场景广泛,它主要解决的是并发压力、故障转移和系统扩展性等问题,以下是负载均衡技术在Web应用中的具体应用场景:

1、解决并发压力

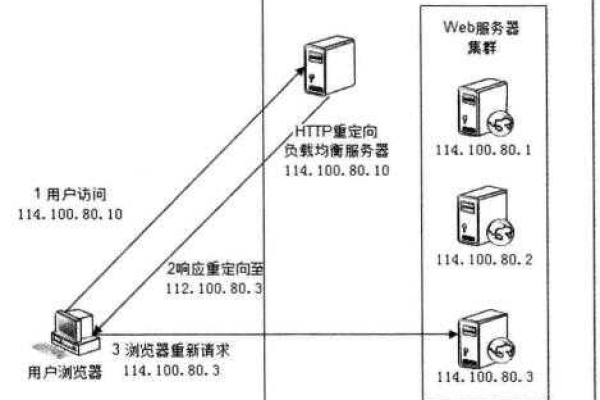

提高处理性能:通过将请求分发到多个服务器上,负载均衡有助于提高Web应用的处理能力,增加吞吐量,加强网络处理能力。

流量分发:对于访问量高的业务,负载均衡能够有效地将流量分发到多台后端服务器上,避免单个服务器因过载而崩溃。

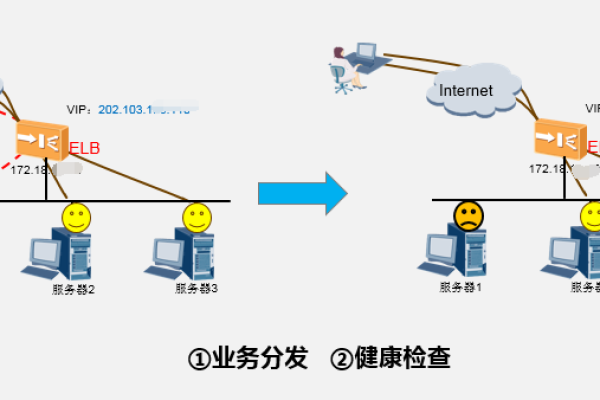

2、提供故障转移

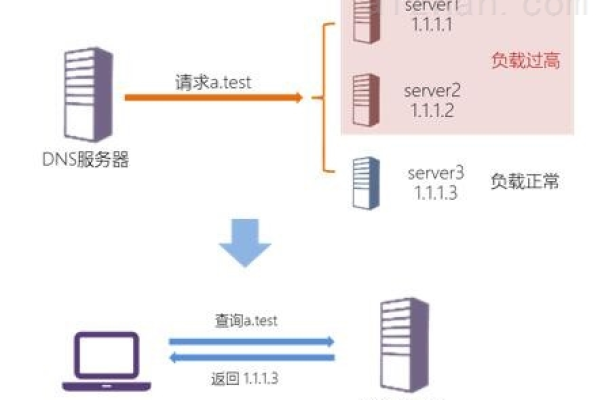

实现高可用性:当其中一部分后端服务器出现故障时,负载均衡器可以自动将流量转移到健康的服务器上,确保服务的持续可用性。

消除单点故障:负载均衡技术通过冗余部署,避免了单点故障对整个系统的影响,提升了应用的稳定性。

3、灵活扩展系统

动态调整资源:根据实际的访问压力,可以通过添加或减少服务器数量来动态调整系统资源,以应对不同的访问需求。

无缝升级:在进行系统维护或升级时,负载均衡器可以暂时将流量引导至其他服务器,从而实现无缝升级,无需中断服务。

4、优化用户体验

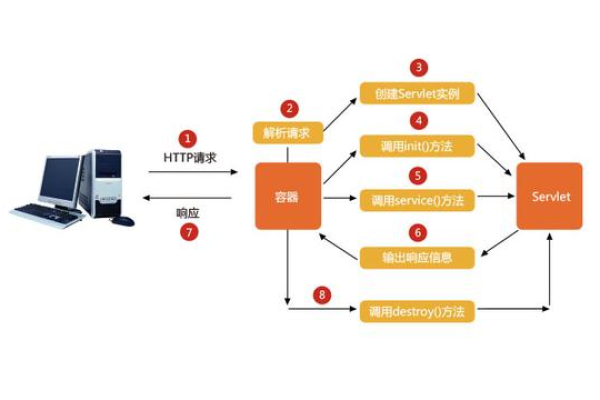

加速响应速度:通过智能算法分配请求,负载均衡可以缩短用户的等待时间,提高访问速度。

保持会话状态:某些负载均衡器支持会话持久性,即使用户请求被分发到不同的服务器,也能保持用户的会话状态不丢失。

5、节约成本

资源利用率最大化:通过合理的负载分发,可以最大化利用每台服务器的资源,避免资源的浪费。

降低硬件投资:通过负载均衡,可以使用性价比更高的服务器集群替代昂贵的大型机。

6、增强安全性

分散攻击流量:在面临DDoS等网络攻击时,负载均衡器能够分散攻击流量,保护后端服务器不受攻击。

集中安全管理:可以在负载均衡层面集中配置安全策略,简化后端服务器的安全管理工作。

7、支持地理位置优化

就近分发请求:负载均衡可以根据用户的地理位置,将请求路由到距离用户最近的服务器,减少延迟。

8、分发

缓存静态内容:负载均衡器可以将经常访问的静态内容缓存起来,加快内容的分发速度。

在深入探讨了负载均衡在Web应用中的多样化应用场景后,可以进一步了解负载均衡技术的一些高级应用,全局服务器负载均衡(GSLB)能够在不同地理位置的服务器之间分配流量,这对于跨国公司或全球服务非常重要,基于内容的路由可以根据请求的内容或应用层的信息来决定最佳的服务器选择,这在一些复杂的应用场景中非常有用,随着云计算和容器技术的发展,负载均衡也与这些技术相结合,提供了更加灵活和高效的服务模式。

本站发布或转载的文章及图片均来自网络,其原创性以及文中表达的观点和判断不代表本站,有问题联系侵删!

本文链接:http://www.xixizhuji.com/fuzhu/6904.html