cpu与存储芯片的连接

- 行业动态

- 2025-02-12

- 10

CPU与存储芯片的连接是计算机系统中至关重要的一环,它涉及到数据的传输、存储和处理,以下是关于CPU与存储芯片连接的详细解释:

1、单块存储芯片与CPU的连接

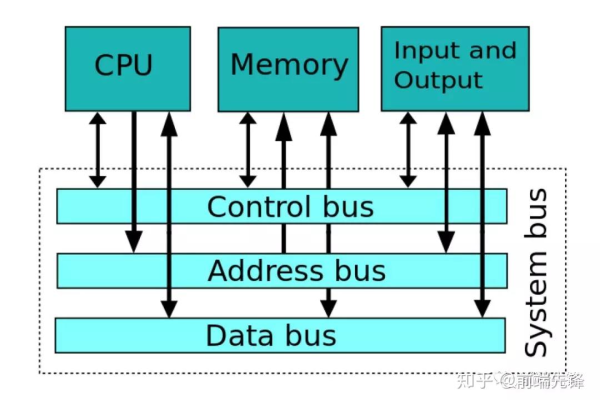

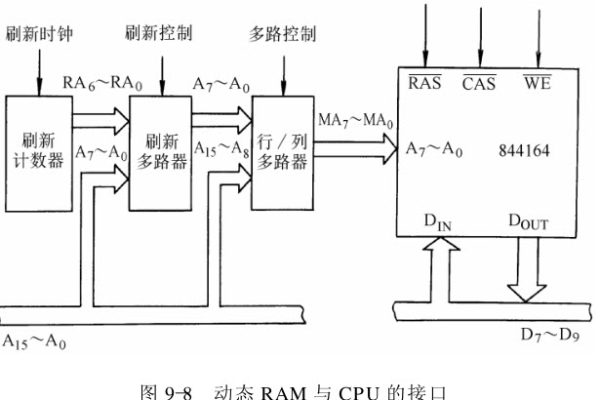

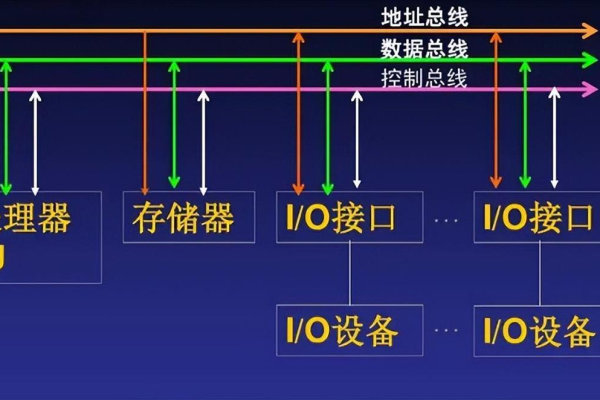

地址线连接:CPU通过地址线来指定寻址存储单元的端口地址,通常将低位地址线(如A0~A7等)与存储芯片的地址线相连,以选择芯片内的特定存储单元(字选),若存储芯片有13根地址线A0~A12,可寻址8K个存储单元,那么CPU的相应低位地址线就与之对应连接。

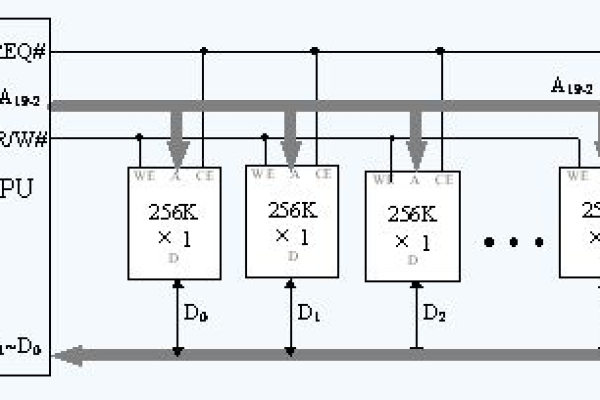

数据线连接:数据线用于在CPU和存储芯片之间传输数据,如果存储芯片的数据位数与CPU的数据位数相匹配,则可直接连接;若不匹配,可通过位扩展等方式使数据位数相等后再连接,当CPU数据线为8位,而存储芯片数据线为4位时,可将两个4位的存储芯片并联,实现8位数据的传输。

控制线连接:包括片选信号线(CS)、读/写控制线(WE)等,片选信号用于选择特定的存储芯片进行读写操作,只有当片选信号有效时,CPU才能对该存储芯片进行访问;读/写控制线则决定数据的传输方向,高电平时CPU从存储芯片读取数据,低电平时CPU向存储芯片写入数据。

2、多块存储芯片与CPU的连接

位扩展:若单块存储芯片的字长小于CPU数据总线的宽度,可采用位扩展来增加存储字长,使用8片8K×1位的存储芯片组成一个8K×8位的存储器,各存储芯片的地址线、片选信号线和读写控制线相应并联,而数据线则分别引出,作为CPU数据线的不同位。

字扩展:当需要扩展主存字数时,可使用字扩展,用4片16K×8位的RAM芯片组成64K×8位存储器,对于字扩展,有线选法和译码器片选法两种方法来产生片选信号。

线选法:将CPU的高位地址线直接连接到各个存储芯片的片选端,通过不同的地址线组合来选择不同的存储芯片,但这种方法需要的地址线较多,且地址空间不连续。

译码器片选法:使用译码器对CPU的高位地址进行译码,产生片选信号,译码器的输出端连接到存储芯片的片选端,通过译码器的不同输出状态来选择相应的存储芯片,这种方法可以节省地址线,且地址空间相对连续。

字位同时扩展:既增加存储字的数量,又增加存储字长,用8片16K×4位的RAM芯片组成64K×8位存储器,每两片16K×4位的芯片构成一组16K×8位的存储器,再用4组这样的芯片构成64K×8位存储器,需要使用译码器来产生片选信号,以选择不同的组和芯片。

CPU与存储芯片的连接方式多样,包括单块和多块存储芯片的连接,以及位扩展、字扩展和字位同时扩展等方法,这些连接方式共同确保了计算机系统能够高效、准确地进行数据传输和存储。