CPU存储器总线在现代计算机架构中扮演着怎样的关键角色?

- 行业动态

- 2025-01-23

- 4749

CPU存储器总线是连接CPU与 存储器的数据传输通道,负责在它们之间传递地址、数据和控制信号,以实现数据的读写操作,其性能对计算机整体运行速度有重要影响。

CPU 存储器总线是连接 CPU 和主存储器的重要通道,在计算机系统中起着关键作用,以下是关于它的详细介绍:

1、定义与组成

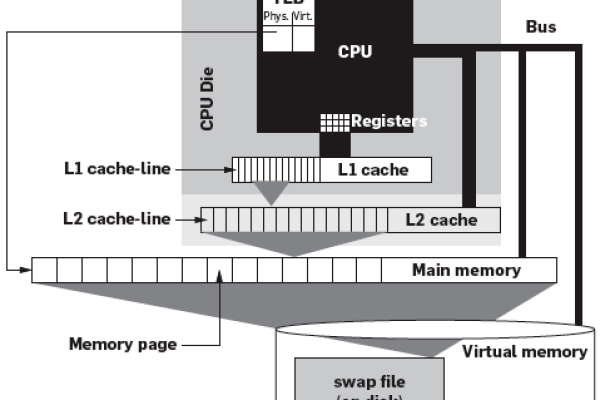

定义:存储总线是指中央处理器 CPU 通过其与主存储器和高速 I/O 设备传输数据的总线,也被称为局部总线。

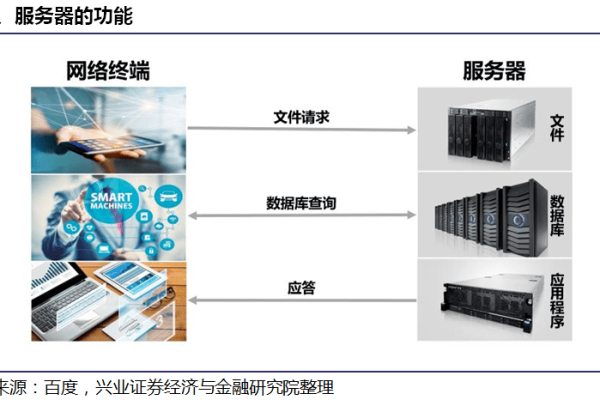

组成:由数据总线、地址总线和控制总线三组传输线路组成。

2、各总线功能

数据总线(Data Bus):用于在 CPU 与主存储器以及 I/O 设备之间传输数据信息,它是双向的,既可以将 CPU 的数据传送到主存或 I/O 设备上,也可以将数据从主存或 I/O 设备传送到 CPU,数据总线的宽度决定了 CPU 与外部数据传输的速度和能力,32 位的数据总线一次可以并行传递 32 位的二进制码。

地址总线(Address Bus):用于传送 CPU 发出的地址信息,以指明寻址存储单元的地址或者 I/O 设备的端口地址,地址总线是单向的,只能从 CPU 向外部传送地址信息,以确定数据总线上传输的数据的来源或去向,地址总线的宽度决定了 CPU 的寻址能力,如 32 位地址总线可以寻址 4GB 的内存空间。

控制总线(Control Bus):用来传送控制信号,包括存储器和 I/O 设备的读写信号、响应信号、时序信号等,以实现对外部设备的有效控制和管理,控制总线是双向的,信号可以从 CPU 发往存储器或 I/O 设备,也可以从这些设备发回 CPU,以确保数据的正确传输和操作的协调进行。

3、工作原理

当 CPU 需要从存储器读取数据时,首先通过地址总线发送要访问的存储单元的地址信息,然后通过控制总线发出一个 “读” 信号,这个地址信息和读信号会被传送到主存储器,主存储器接收到后,会将指定地址连续的几个存储单元中的数据读出,并通过数据总线发送给 CPU,CPU 就可以从数据总线上获取所需的数据。

当 CPU 需要向存储器写入数据时,同样先通过地址总线发送存储单元的地址信息,再通过控制总线发出 “写” 信号,同时将数据放到数据总线上,主存储器接收到这些信息后,会将数据总线上的数据写入到指定地址的存储单元中。

4、总线速度与性能影响

总线的速度对计算机系统的性能有着重要影响,总线的带宽决定了系统的数据传输速率,带宽越高,数据传输速度越快,系统的整体性能也就越高,随着计算机技术的不断发展,总线的速度也在不断提高,以满足日益增长的数据处理需求。

5、应用实例

在中、小型计算机中,由于 CPU 工作期间要不断地取指令、取操作数、送结果等,CPU 与主存之间的信息流量特别大,因此在这两个最繁忙的部件之间增设了一组存储总线,以提高数据传输效率。

6、总线架构类型

单总线架构:早期计算机常采用的结构,使用单一总线连接各个部件,结构简单,但存在性能瓶颈,所有信号都要经过同一个共享总线,不允许两个以上部件同时传输信号。

多总线架构:现代计算机大多采用的结构,将高速部件和低速部件分开连接,减少高速部件对低速部件的等待,增加多条总线使数据可以同时在多个部件之间传输,提高了系统的性能和可扩展性。

7、前端总线与后端总线

前端总线(FSB):是 CPU 与北桥芯片之间连接的总线,负责 CPU 与内存之间的数据传输,其频率直接影响 CPU 与内存之间的通信速度,进而影响系统性能。

后端总线(BSB):也叫本地总线或片内总线,是 CPU 芯片内部独立使用的总线,用于 CPU 芯片内部核心、Cache 之间的通信,不需要占用芯片外的系统总线,提高了 CPU 内部的数据传输效率。

8、总线仲裁:由于总线具有共享性和独占性,同一时刻只能允许一个部件使用总线进行数据传输,因此需要总线仲裁来决定哪个部件可以获得总线的控制权,常见的总线仲裁方式有集中式仲裁和分布式仲裁等。

CPU 存储器总线作为连接 CPU 与主存储器的关键通道,其重要性不言而喻,随着计算机技术的不断进步,总线技术也将不断创新和发展,为构建更高效、更可靠的计算机系统提供有力支持。

本站发布或转载的文章及图片均来自网络,其原创性以及文中表达的观点和判断不代表本站,有问题联系侵删!

本文链接:http://www.xixizhuji.com/fuzhu/398987.html