CPU如何实现与存储器的数据交互?

- 行业动态

- 2025-01-24

- 2494

CPU 通过存储器总线(Memory Bus)与 存储器进行连接,以便进行数据和指令的读写操作。

在计算机系统中,CPU 通过多种方式访问存储器,以下是详细内容:

1、通过地址总线和数据总线:

地址传送:CPU 将要访问的存储器地址传送到地址总线上,当 CPU 需要读取内存中某个存储单元的数据时,它会将该存储单元的地址信息发送到地址总线上,以便寻址。

存储器选择:存储器根据地址总线上的地址信号选择要读写的存储单元,并将其数据或指令传送到数据总线上,在上述例子中,内存接收到地址信息后,会定位到对应的存储单元,并将该存储单元中的数据输出到数据总线上,以供 CPU 读取。

数据传送:CPU 通过数据总线从存储器中读取或写入数据或指令,完成对内存的访问操作,CPU 执行的是读操作,那么数据会从数据总线上传输到 CPU 内部;如果是写操作,数据则会从 CPU 传输到数据总线上,再由存储器接收并存储到相应的存储单元中。

控制信号传送:存储器总线还需要传输一些控制信号,如读写控制信号、时钟信号和同步信号等,以便存储器和 CPU 之间可以正确地协调和通信,读写控制信号用于指示当前是读操作还是写操作,时钟信号和同步信号则确保数据传输的准确性和稳定性。

2、直接寻址和间接寻址:

直接寻址:CPU 直接访问存储器中的某个地址,汇编指令MOV AX, [0x1234] 将会从存储器地址0x1234 处读取数据并存入寄存器 AX 中。

间接寻址:CPU 通过一个地址来访问另一个地址,汇编指令MOV AX, [BX] 将会从存储器地址 BX 中读取一个地址,然后再从该地址所指向的存储器中读取数据,并将读取的数据存入寄存器 AX 中。

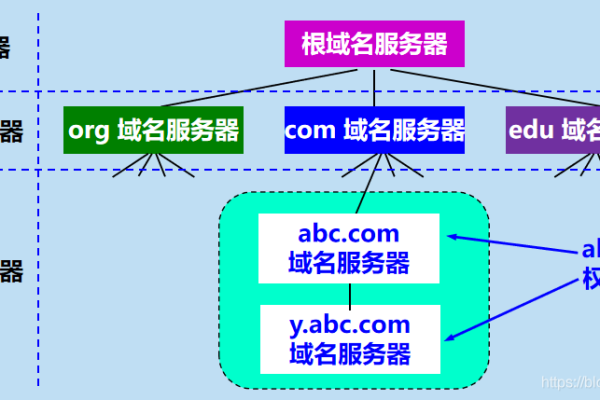

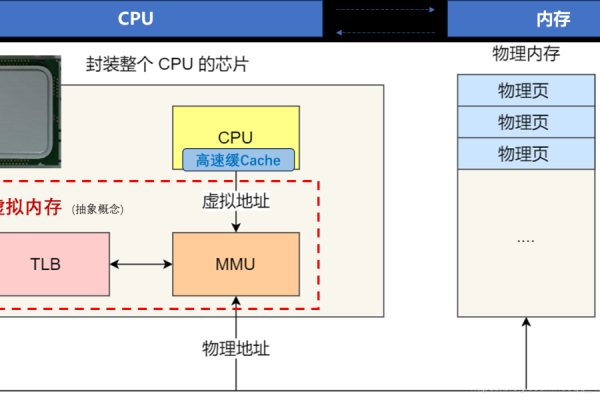

3、段页式存储管理:

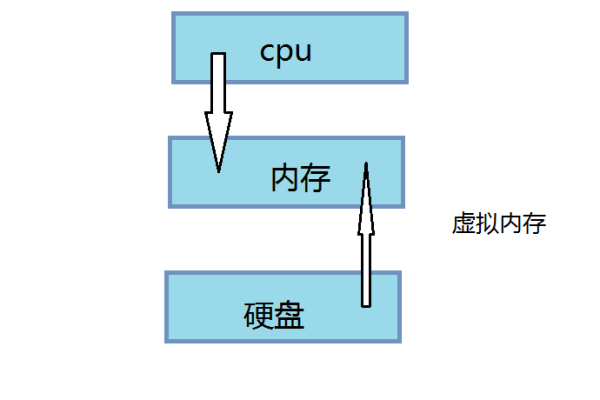

提供逻辑地址:程序员交给 CPU 的是逻辑地址,需要经过虚实地址转换才能找到该虚拟地址所对应的数据实际存放的位置。

虚实地址转换:虚页号与实页号的对应关系存在页表(页表存在主存)中,比较活跃的页表项存在 TLB 中(TLB 相当于专用于存页表项的 Cache),先查 TLB,若 TLB 不命中,再查页表,若页表还不命中,说明该页面还未调入主存,需发出缺页中断,从辅存中调入并更新页表和 TLB。

访 Cache-主存:得到物理地址后,需要访问 Cache-主存体系以操作相应的数据,先访问 Cache,若 Cache 未命中,说明该块在主存中,需要先把该块调入 Cache 再处理,或者边调入 Cache 边处理。

4、DMA(Direct Memory Access):

准备阶段:CPU 会对 DMA 控制器和 I/O 接口进行初始化,配置 DMA 内存缓冲区的首地址、传输方向、交换量等参数,以及 I/O 设备的寻址信息。

传输请求:设备接口向 DMA 控制器发送 “DMA 请求”,DMA 控制器向 CPU 申请总线占用,CPU 批准使用总线后,让出一个或多个总线周期用于数据传输。

数据传送:DMA 控制器掌管总线控制权,按照设定的传输模式和寻址模式,将数据从源地址传输到目的地址,在传输过程中,CPU 停止访问内存,无法执行需要占用总线的指令。

善后处理:当传送结束时,DMA 控制器向 CPU 发送一个传输完成的中断,CPU 重新接管总线的控制权。

5、通过寄存器和段机制:

实模式下的访问:在实模式下,8086 CPU 用 CS:IP 寄存器来表示代码段,DS:DI 寄存器来表示数据段,ES:SI 寄存器用于额外的数据段需求,SS:SP 寄存器用于栈段,还有 CX 寄存器用于存储循环次数等,通过这些寄存器的组合,可以实现对不同段的访问和数据的读写。

保护模式下的访问:32 位以上的微处理器系统中通常还需要全局描述符表等机制来实现对内存的访问和管理,全局描述符表中的每个描述符定义了内存中的一个段的信息,包括段的基地址、大小、权限等,CPU 通过段选择子和偏移量来计算线性地址,然后通过分页机制将线性地址转换为物理地址,从而实现对内存的访问。

CPU访问存储器有多种方式,不同的方式适用于不同的场景和需求,这些方式共同构成了计算机系统中CPU与存储器之间的复杂而高效的交互机制。

本站发布或转载的文章及图片均来自网络,其原创性以及文中表达的观点和判断不代表本站,有问题联系侵删!

本文链接:http://www.xixizhuji.com/fuzhu/398437.html