CPU访问存储器的时间是如何确定的?

- 行业动态

- 2025-01-16

- 4850

CPU访问存储器时间是指中央处理器从存储器中读取或写入数据所需的时间,包括地址传送、命令发送、数据传输等过程。

CPU访问存储器的时间是一个复杂且多因素共同作用的结果,它直接影响着计算机系统的整体性能,以下是对CPU访问存储器时间影响因素的详细解析:

一、存储器类型与层次结构

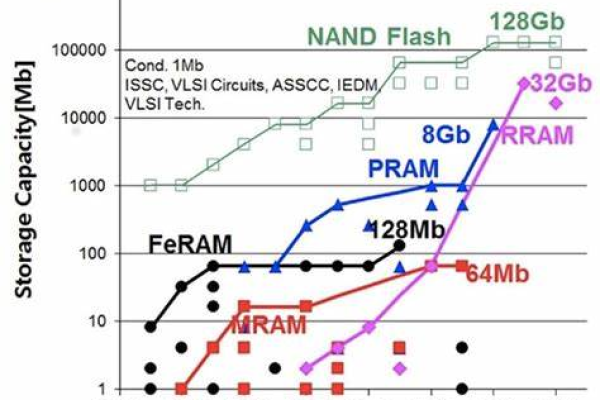

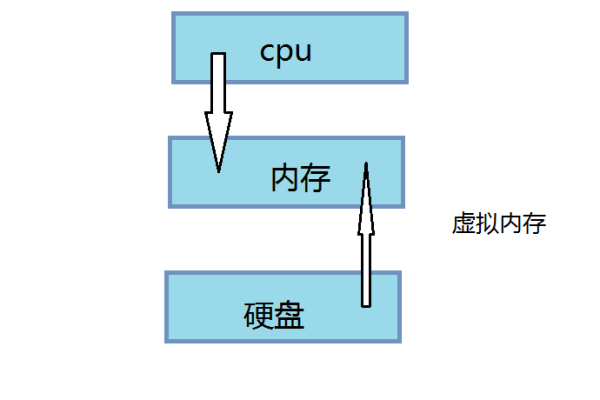

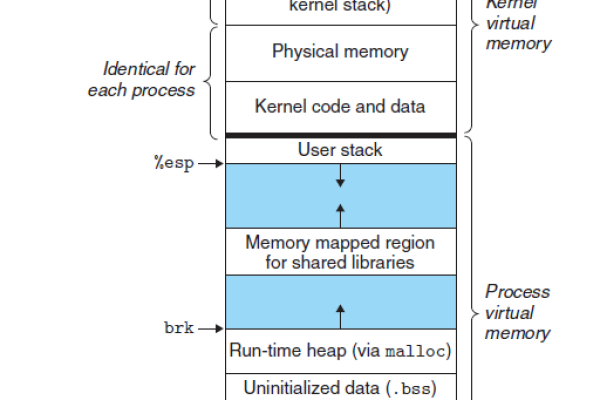

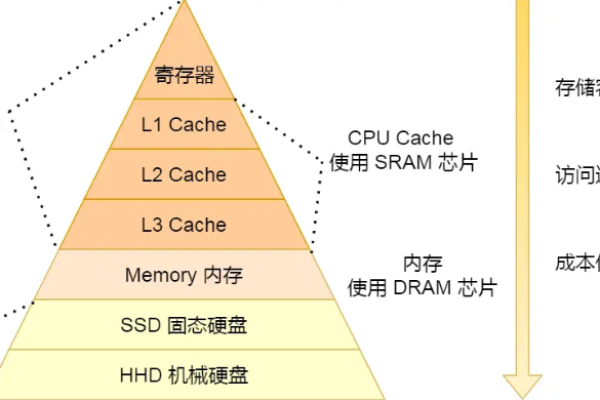

1、存储器类型:不同类型的存储器具有不同的访问速度,RAM(随机存取存储器)的访问时间通常比硬盘驱动器(HDD)短得多,而Cache(高速缓存)的访问时间则更短。

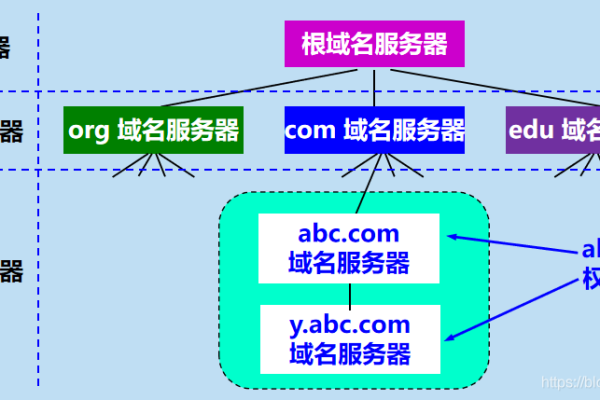

2、存储器层次结构:现代计算机系统通常采用多级Cache(如L1、L2、L3缓存)来减少访问主存储器的次数,从而降低访问时延,多级Cache的设计使得CPU在需要数据时,首先检查最近的缓存级别,如果未命中,再依次检查更高级别的缓存,最后才访问主存储器。

二、存储器容量与地址线数量

1、存储器容量:虽然存储器容量本身并不直接决定访问时间,但大容量存储器可能需要更多的地址线来寻址,这可能会间接影响访问时间,这种影响通常较小,因为地址线的增多主要影响的是地址空间的大小,而非访问速度。

2、地址线数量:地址线的数量决定了存储器的地址空间大小,理论上,地址线数量越多,存储器的容量越大,但同时也会稍微增加访问时间,因为需要更多的地址线来寻址,这种影响在实际应用中并不显著,因为地址线的增多主要是为了满足大容量存储的需求。

三、存储器访问方式与总线带宽

1、存储器访问方式:存储器可以以随机存取(RAM)或顺序存取(如硬盘驱动器)的方式进行访问,随机存取存储器通常具有较短的访问时间,而顺序存取存储器则可能具有较长的访问时间。

2、总线带宽:CPU与存储器之间的数据传输必须通过总线进行,总线带宽越高,数据传输速度越快,从而可以降低存储器访问时延,高内存带宽支持更快的数据传输,减少访问时延。

四、存储器控制器性能

存储器控制器负责管理存储器的访问操作,其性能和效率也会影响存储器访问时延,高效的存储器控制器能够快速响应CPU的访问请求,并优化数据传输过程。

五、其他因素

1、指令提取与解码时延:CPU从存储器中读取指令到将其放入指令寄存器的时间,以及将从内存中读取的指令翻译成CPU能够理解的操作的时间,都会影响CPU访问存储器的总时间。

2、执行时延与写回时延:CPU实际执行指令所需的时间以及执行完指令后将结果写回寄存器或存储器的时间,也是CPU访问存储器时间的重要组成部分。

CPU访问存储器的时间受到多种因素的影响,包括存储器类型与层次结构、存储器容量与地址线数量、存储器访问方式与总线带宽、存储器控制器性能以及其他与CPU执行相关的时延等,为了提高CPU访问存储器的效率,可以采取优化缓存策略、提高内存子系统性能、使用高效的并行算法等措施。

本站发布或转载的文章及图片均来自网络,其原创性以及文中表达的观点和判断不代表本站,有问题联系侵删!

本文链接:http://www.xixizhuji.com/fuzhu/394566.html