存储器字位扩展实验的核心难点你攻克了吗?

- 行业动态

- 2025-04-20

- 1

本实验通过字扩展与位扩展技术,利用多片存储器芯片实现存储容量及数据位的提升,采用EDA工具完成电路设计与仿真,验证了地址分配、逻辑控制及数据读写功能,实验结果表明扩展方案可行,分析了时序稳定性与信号干扰因素,总结了存储器扩展在计算机系统中的实际应用价值。

实验目的

存储器字位扩展是计算机组成原理中的重要实验,旨在通过扩展存储器的字长(位扩展)或容量(字扩展),掌握地址分配、片选信号设计及数据线连接方法,本实验通过实际操作,帮助读者深入理解存储器扩展的基本原理,提升硬件设计与调试能力。

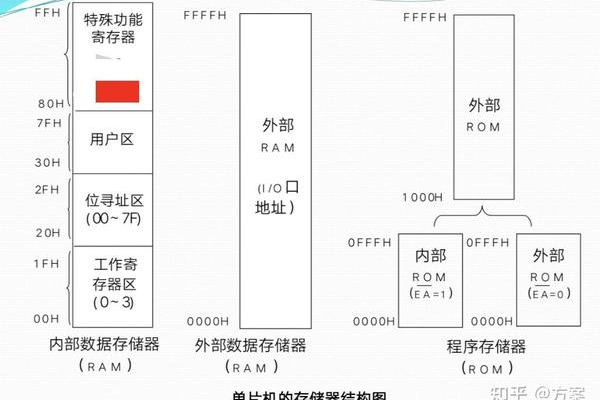

实验原理

位扩展(数据位扩展)

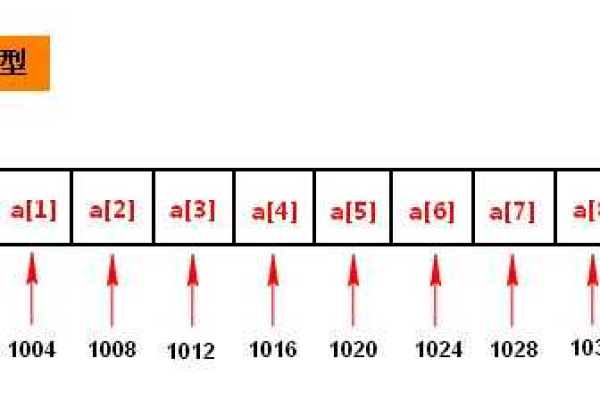

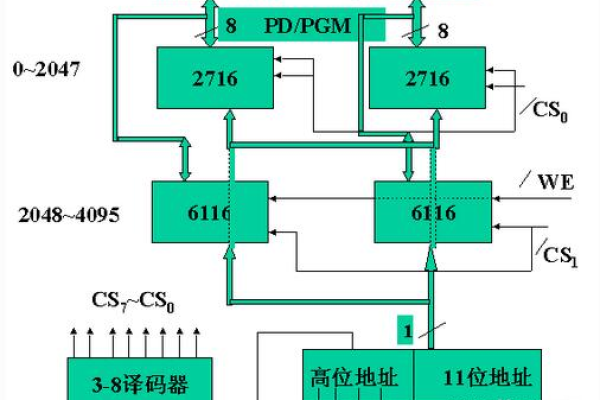

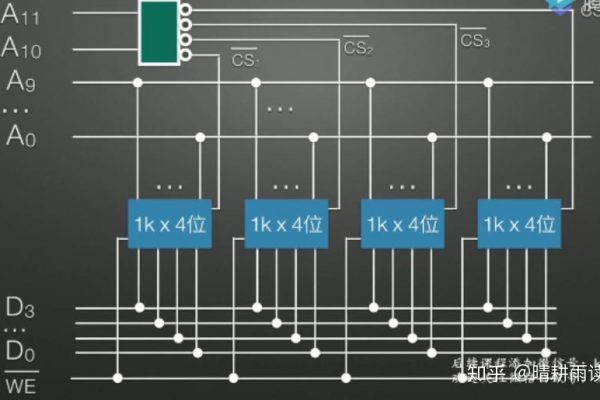

当存储器的数据位数不足时,需将多片存储芯片的数据线并联,若单颗芯片数据宽度为4位,需用两片芯片并联实现8位数据输出,所有芯片的地址线和控制线(如读/写信号)需统一连接,仅数据线分开输出高低位。字扩展(容量扩展)

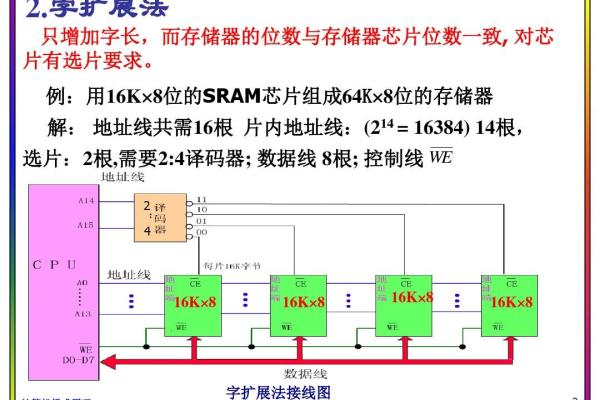

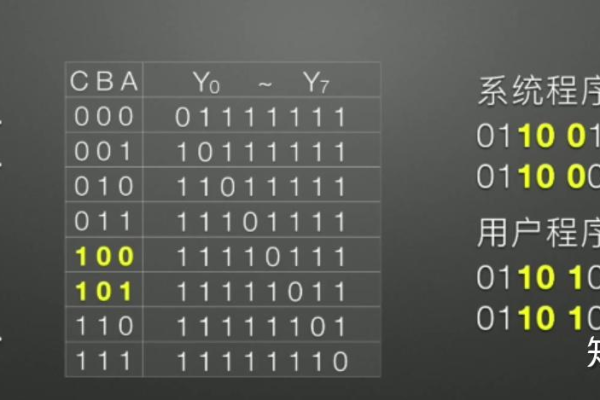

若需扩大存储容量,需通过地址译码器分配不同芯片的片选信号,使用3-8译码器(74LS138)将地址空间划分为多个区间,每片芯片负责一段地址范围,数据线和控制线共用,地址线高位接入译码器,低位接入芯片地址引脚。

实验设备与器材

- 静态随机存储器(SRAM)芯片:6116(2K×8位)

- 地址译码器:74LS138

- 逻辑电平开关、LED显示模块

- 数字实验箱、万用表、连接线

实验步骤

位扩展实现

- 将两片6116芯片的地址线(A0~A10)、读/写控制线(WE)并联。

- 第一片芯片的数据线(D0~D7)接至低4位,第二片接至高4位。

- 输入地址信号,通过LED验证高低位数据是否独立读写。

字扩展实现

- 使用74LS138译码器,将高位地址线(A11~A13)接入译码器输入端。

- 译码器输出端(Y0~Y7)分别连接至8片6116的片选信号(CS)。

- 向不同地址区间写入数据,确认各芯片能否按地址范围独立响应。

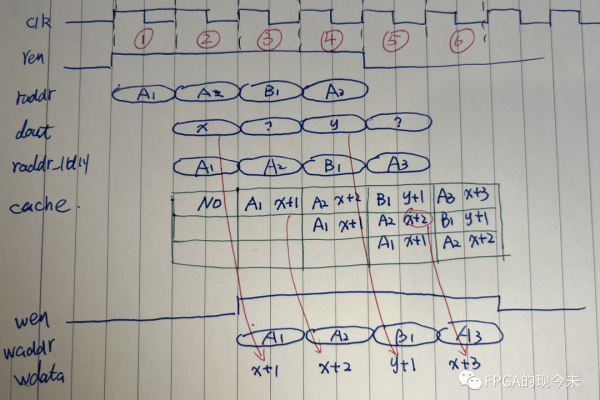

联合扩展测试

- 结合位扩展与字扩展,构建总容量为16K×16位的存储器系统。

- 编写测试程序,按地址顺序写入特定数据(如0xAA、0x55),读取并验证数据一致性。

实验结果与分析

位扩展验证

- 地址0x0000写入0x0F,读取结果为低4位0x0F、高4位0x00,符合预期。

- :数据线并联后,高低位可独立操作,位扩展成功。

字扩展验证

- 向地址0x1000写入数据0x55,仅第二片芯片响应,其他片选信号保持高电平。

- :译码器能准确分配地址空间,字扩展逻辑正确。

联合扩展验证

- 地址0x2000~0x3FFF区间写入数据0xAAAA,读取结果一致,无冲突。

- 故障排除:初始连接时发现地址线A12接触不良,经万用表检测后修复。

实验结论

通过位扩展与字扩展的结合,成功将多片小容量存储器芯片扩展为大容量、宽数据位的存储系统,实验表明,地址译码器与数据线并联是扩展的核心,需严格检查硬件连接与信号时序。

注意事项

- 芯片电源极性不可接反,避免烧毁器件。

- 片选信号需保持唯一性,防止多芯片同时响应导致数据冲突。

- 地址线连接顺序需与译码逻辑匹配,建议提前绘制地址分配表。

参考文献

- 《计算机组成原理(第5版)》,唐朔飞,高等教育出版社

- 《数字逻辑与计算机设计》,M. Morris Mano,机械工业出版社

- 芯片手册:6116 SRAM Datasheet, 74LS138 Decoder Datasheet

(注:实验数据及结果基于标准实验室环境,实际操作中可能因器件差异需调整参数。)