Flash存储器究竟如何实现高效数据存储?

- 行业动态

- 2025-04-20

- 1

Flash存储器基于浮栅晶体管结构,利用电压驱动电荷隧穿实现数据存储,其单元通过浮栅是否捕获电荷区分0/1状态,擦除时需以区块为单位释放电荷,NOR型支持快速随机访问,NAND型侧重高密度存储,广泛应用于移动设备和固态硬盘。

Flash存储器工作原理详解

在数字时代,几乎所有电子设备都离不开存储技术,而Flash存储器作为非易失性存储的核心组件,凭借其快速读写、低功耗、高可靠性等特性,占据了从U盘到智能手机、固态硬盘(SSD)的庞大市场,本文将以通俗易懂的方式,解析Flash存储器的工作原理,帮助读者理解这一技术背后的科学逻辑。

Flash存储器的物理基础:浮栅晶体管

Flash存储器的核心单元是浮栅场效应晶体管(Floating Gate MOSFET),它与普通MOSFET的关键区别在于多了一个被绝缘层(二氧化硅)包裹的浮栅层,就像一座“电子水库”。

- 写入数据(编程):向控制栅施加高电压(通常10-20V),电子通过量子隧穿效应(F-N隧穿)或热电子注入进入浮栅层,改变晶体管的阈值电压,晶体管代表“0”状态。

- 擦除数据:施加反向电压,将浮栅中的电子拉出,恢复晶体管到“1”状态。

- 读取数据:通过检测晶体管的导通状态判断存储值,若浮栅中有电子,阈值电压升高,晶体管不导通即为“0”;反之则为“1”。

存储架构:NAND与NOR的差异

Flash存储器分为NAND和NOR两种类型,两者在结构与用途上截然不同:

| 特性 | NAND Flash | NOR Flash |

|---|---|---|

| 结构 | 串联晶体管,高密度 | 并联晶体管,独立寻址 |

| 读写速度 | 页读写快,随机读慢 | 随机读取快,写入慢 |

| 容量与成本 | 大容量、低成本 | 小容量、高成本 |

| 应用场景 | U盘、SSD、手机存储 | 嵌入式系统、固件存储 |

NAND Flash通过堆叠存储单元(如3D NAND技术)实现容量突破,而NOR Flash因支持XIP(就地执行)特性,常用于存储启动代码。

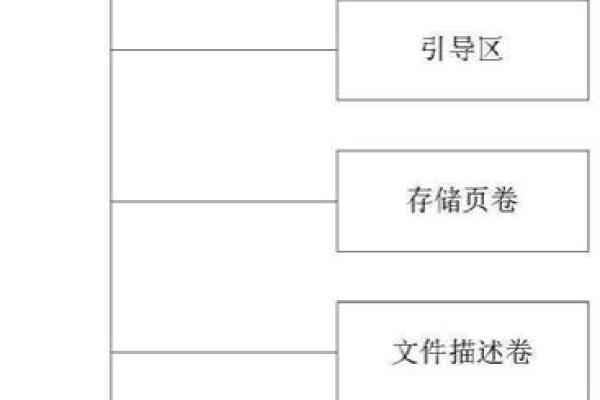

数据管理:页、块与损耗均衡

Flash存储器以页(Page)和块(Block)为单位操作:

- 页:最小写入单位(通常4KB-16KB),写入前需擦除。

- 块:最小擦除单位(通常包含64-256页),擦除次数有限(NAND约1万-10万次)。

由于写入前必须擦除的特性,Flash控制器需通过损耗均衡算法(Wear Leveling)动态分配数据位置,避免局部块过早失效,SSD控制器会记录每个块的擦除次数,优先使用低磨损块。

关键技术挑战与解决方案

- 氧化层磨损

频繁擦写会导致绝缘层退化,最终电子泄漏,现代Flash通过纠错码(ECC)和冗余存储修复数据错误。 - 数据干扰

高密度存储下,邻近单元的电荷可能影响当前单元。读取电压校准技术可动态调整阈值,减少误判。 - 性能优化

采用SLC(单层单元)、MLC(双层)、TLC(三层)和QLC(四层)技术,在容量与寿命之间平衡,SLC耐用性最高,而QLC成本最低。

Flash存储器的应用场景

- 消费电子:智能手机、相机存储卡

- 数据中心:SSD取代传统机械硬盘

- 物联网设备:低功耗嵌入式存储

- 汽车电子:自动驾驶系统数据记录

据市场研究机构TrendForce数据,2025年全球NAND Flash市场规模已超600亿美元,3D NAND占比超过90%,技术迭代持续推动容量提升。

延长Flash寿命的实用建议

- 避免频繁写入临时文件(如浏览器缓存)。

- 启用设备的TRIM指令(SSD专用),标记无效数据块。

- 预留预留空间(Over-Provisioning),通常建议保留7%-25%未分配空间。

- 定期备份重要数据,防止突发故障。

引用说明

- 《半导体存储器技术》(作者:李志坚,清华大学出版社)

- JEDEC固态技术协会标准 JESD230D

- 三星电子《3D NAND技术白皮书》

- IEEE论文《Flash Memory Reliability: A Review of Current Issues》