存储器线路排列组如何影响性能提升?

- 行业动态

- 2025-04-21

- 2

存储器中的线路排列组指存储单元的布局与连接方式,通过行列线路实现寻址和数据传输,影响存储器的存取速度和效率,优化排列结构可提升存储密度与性能,常见设计包括矩阵式排布和分层式分组。

在计算机系统中,存储器的性能与结构设计直接影响整体运行效率。存储器的线路布局(线)和排列组(Bank、Rank、Chip等)是核心技术要点,以下从原理、设计逻辑及实际应用展开分析,帮助用户全面理解其工作机制。

存储器的基础架构:从单元到系统

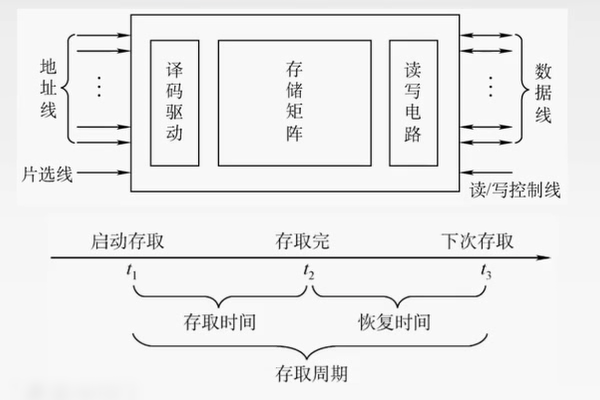

存储器的基本组成单元是存储单元(Memory Cell),每个单元通过晶体管与电容存储二进制数据,多个存储单元构成存储阵列(Memory Array),并通过行列地址线(Word Line、Bit Line)连接。

- 行地址线(Word Line):激活特定行的存储单元。

- 列地址线(Bit Line):读取或写入数据时选择对应列。

这种行列交叉的矩阵结构,使得存储器能够通过坐标定位快速访问数据。

存储器的“线”:信号传输的核心通道

存储器的“线”不仅包括物理电路,还涉及数据传输的逻辑通道,主要分为以下两类:

物理线路:硬件连接的“血管”

- 数据总线(Data Bus):传输实际数据,宽度决定每次可传输的比特数(如64位)。

- 地址总线(Address Bus):传递存储单元的位置信息,宽度决定可寻址空间(如32位总线支持4GB寻址)。

- 控制总线(Control Bus):发送读写指令、时钟信号等控制命令。

逻辑通道:性能优化的关键

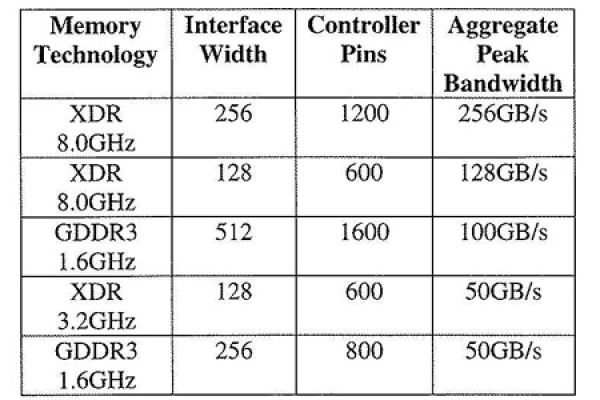

现代存储器采用多通道架构提升带宽。

- 双通道(Dual Channel):同时使用两条内存模块,带宽翻倍。

- 四通道(Quad Channel):高端服务器常用,进一步减少延迟。

排列组设计:提升效率的层级结构

存储器的排列组通过分层管理,实现高效存取与容量扩展,典型层级包括:

Bank分组:并行操作的基石

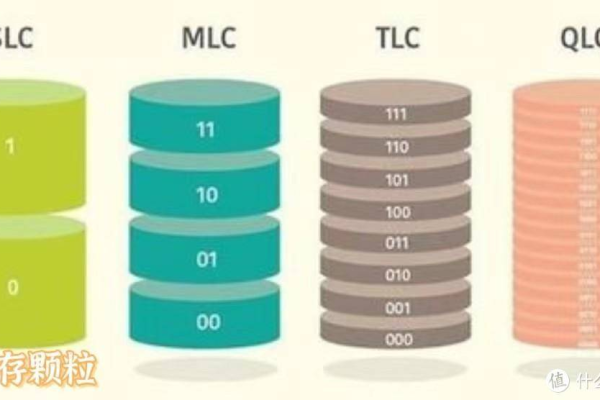

- Bank:存储器内部被划分为多个独立区域,每个Bank可同时执行操作,DDR4内存通常含16个Bank。

- Bank Group:DDR4引入的概念,将Bank分组管理,进一步缩短切换延迟。

Rank与Chip:模块化扩展方案

- Rank:一组内存芯片(Chip)的集合,共享控制信号,单Rank模块占用64位总线,双Rank模块通过分时复用提高容量。

- Chip:单个存储芯片,内部包含多个Bank,8Gb芯片可能由8个1Gb的Bank组成。

排列组的优化技术与应用场景

交错存取(Interleaving)

通过将数据分布到不同Bank或Rank,实现并行读取,CPU访问Bank 1时,Bank 2可预加载下一批数据,减少等待时间。

3D堆叠技术

采用TSV(硅通孔)垂直堆叠多层存储单元,突破平面布局限制,三星的HBM(高带宽内存)即通过3D堆叠实现超高带宽。

实际应用对比

| 配置方案 | 带宽提升 | 典型场景 |

|---|---|---|

| 双通道+双Rank | 200% | 游戏PC、图形工作站 |

| 四通道+Bank分组 | 350% | 数据中心、AI服务器 |

如何选择适合的存储器配置?

- 需求优先级:若追求高带宽(如视频剪辑),选择多通道;若需大容量(如数据库),侧重多Rank设计。

- 兼容性验证:主板和CPU需支持对应的通道数与Rank配置。

- 散热与功耗:高密度排列可能增加发热,需匹配散热方案。

参考文献

- JEDEC标准文档:DDR4 SDRAM Specification(JESD79-4B)

- Intel®技术白皮书:《Optimizing Memory Performance for Xeon Processors》

- 三星电子:《3D TSV-Based HBM Development》

基于公开技术资料与行业实践,具体产品参数请以厂商发布信息为准。)