为何存储器映射I/O在系统优化中被严重低估?

- 行业动态

- 2025-04-18

- 1

在计算机体系中,存储器映射I/O(Memory-Mapped I/O,简称MMIO) 是一种通过统一地址空间访问输入输出设备的机制,它将I/O设备的寄存器或缓冲区映射到主内存的地址范围内,使得CPU可以通过读写内存指令(如LOAD和STORE)直接与硬件交互,而无需专用的I/O指令,这种设计简化了硬件与软件的通信方式,同时提升了系统灵活性。

存储器映射I/O的工作原理

存储器映射I/O的核心思想是将I/O设备的物理资源(如控制寄存器、数据缓冲区)与内存地址一一绑定,当CPU需要从某个传感器读取数据时,只需访问特定的内存地址(如0xFFFF0000),这个地址实际对应传感器的数据寄存器,而非物理内存芯片。

地址空间的划分

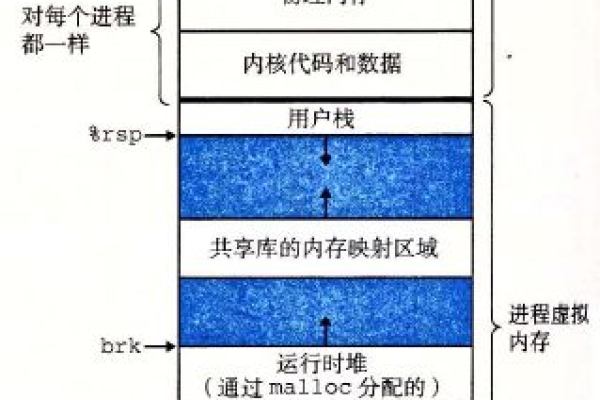

系统内存的一部分地址范围会被预留给I/O设备,32位系统中,若物理内存总大小为4GB,可能将高地址段(如后1GB)分配给各类外设,剩余3GB供程序和数据使用。硬件与内存的无缝交互

CPU无需区分内存和I/O操作,所有访问均通过内存总线完成,向0xFFFF0004写入数据,可能触发显卡更新显示内容;读取0xFFE00000则可能获取键盘输入的状态。

存储器映射I/O的优势

简化编程模型

开发者使用统一的内存读写指令即可操作硬件,无需学习复杂的I/O指令集(如x86的IN和OUT指令),降低了驱动开发的难度。

提高执行效率

直接通过内存总线传输数据,省去了专用I/O指令的解码和执行步骤,CPU的缓存机制可能加速对I/O寄存器的频繁访问。灵活扩展性

新增外设只需分配未使用的内存地址,无需修改CPU指令集或系统架构,这一特性在嵌入式系统和片上系统(SoC)中尤为重要。

存储器映射I/O的挑战

地址冲突风险

若内存分配不当,可能导致I/O设备与物理内存地址重叠,引发数据损坏或系统崩溃,需要严谨的地址管理,通常由操作系统或硬件固件负责。内存保护的复杂性

普通程序可能误操作I/O地址,导致硬件故障,现代操作系统通过内存管理单元(MMU) 限制用户程序对I/O地址的访问权限,仅允许内核态代码操作这些区域。

性能瓶颈

频繁的I/O操作可能占用内存总线带宽,影响内存访问效率,某些场景下,直接内存访问(DMA) 技术会被用来绕过CPU,减少总线争用。

典型应用场景

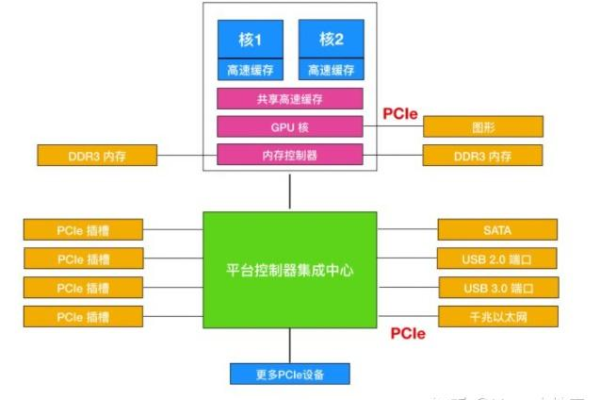

图形处理器(GPU)显存映射

显卡的显存通常映射到系统内存的高地址段,CPU通过写入显存地址更新屏幕内容,而GPU则直接读取这些数据渲染图像。嵌入式系统中的传感器控制

微控制器(如ARM Cortex-M系列)通过存储器映射I/O访问GPIO、ADC、定时器等外设寄存器,实现实时控制。网络接口卡(NIC)数据传输

网卡的数据缓冲区被映射到内存中,操作系统通过读写这些区域收发网络数据包。

与端口映射I/O的对比

另一种I/O访问方式是端口映射I/O(Port-Mapped I/O,PMIO),它使用独立的地址空间和专用指令(如x86的IN/OUT),两者的关键区别如下:

| 特性 | 存储器映射I/O | 端口映射I/O |

|---|---|---|

| 地址空间 | 共享内存地址空间 | 独立的I/O地址空间 |

| 指令类型 | 内存读写指令(如MOV) | 专用指令(如IN/OUT) |

| 访问速度 | 通常更快(利用缓存) | 较慢 |

| 编程复杂度 | 低(与内存操作一致) | 高(需特殊指令) |

| 典型应用 | 通用计算机、嵌入式系统 | 传统x86架构设备 |

技术实现细节

- 硬件支持:芯片组或SoC需要提供地址解码逻辑,将CPU发出的内存地址映射到正确的设备。

- 操作系统角色:内核通过设备树(Device Tree)或ACPI表获取I/O地址信息,并在启动阶段初始化映射关系。

- 驱动程序开发:驱动直接读写映射后的内存地址,通过内存屏障(Memory Barrier)确保操作的原子性与顺序性。

存储器映射I/O通过统一内存与I/O的地址空间,提供了一种高效、直观的硬件交互方式,尽管存在地址管理和安全性的挑战,但其在性能与灵活性上的优势使其成为现代计算机系统的基石,理解这一机制,有助于开发者编写高效驱动,优化系统资源分配,并深入探索计算机体系结构的底层逻辑。

引用说明 参考了《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)、ARM官方文档及Linux内核开发手册。