存储器读写实验中有哪些关键技巧需要掌握?

- 行业动态

- 2025-04-17

- 2

通过存储器读写实验掌握了地址译码与数据存取的基本原理,验证了RAM芯片的读写功能,利用软件/硬件方法测试了存储单元操作时序与信号变化,发现正确读写需满足特定时序要求,实验结果验证了存储器工作原理,加深了对计算机存储机制的理解,为后续系统设计奠定实践基础。

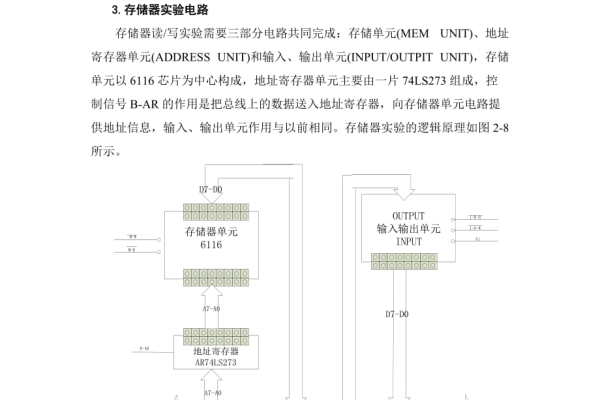

实验原理与目的

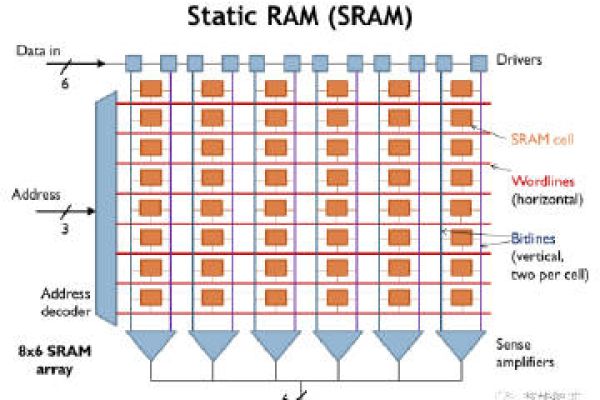

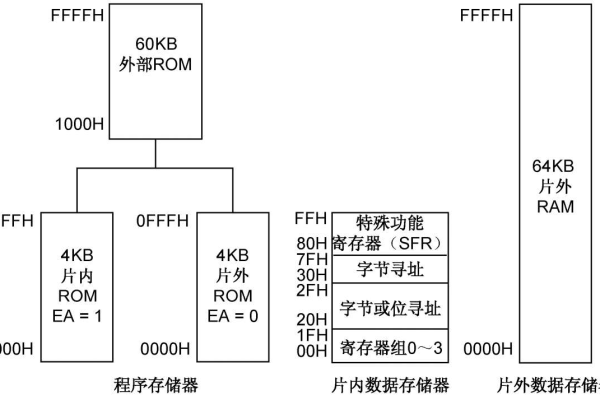

存储器(Memory)是计算机系统中用于存储程序与数据的关键部件,分为RAM(随机存储器)和ROM(只读存储器)两类,本次实验聚焦于RAM的读写操作,目标包括:

- 验证存储单元寻址能力:通过地址总线与数据总线的配合,定位存储单元并完成数据写入/读出。

- 时序匹配验证:测试存储器的读写时序与CPU时钟的同步性。

- 稳定性测试:在不同电压或频率下检测存储器的数据保存能力。

实验通常基于FPGA开发板或单片机(如STM32、8051)实现,结合示波器或逻辑分析仪监测信号波形。

实验步骤与核心操作

硬件连接

- 将存储芯片(如SRAM 62256)的地址总线、数据总线与控制器(如CPU)对应引脚连接。

- 控制信号(如片选CE、写使能WE、输出使能OE)需接入控制器GPIO,确保电平匹配。

- 关键点:检查总线是否存在短路或虚焊,避免信号传输错误。

初始化配置

- 设置控制器时钟频率(如12MHz),配置存储器访问时序参数(如建立时间、保持时间)。

- 示例代码(基于C语言):

void RAM_Init() { MEM_CTRL_REG |= 0x1F; // 配置时序参数 Delay(10); // 等待稳定 }

读写功能测试

- 写入阶段:向指定地址(如0x0000-0x7FFF)写入随机数据(如0xAA、0x55等交替模式)。

- 读取验证:逐地址回读数据,对比写入值与读取值的一致性。

- 异常处理:若数据不匹配,需检查地址译码电路或时序配置。

实验结果与数据分析

| 测试项 | 预期结果 | 实际结果 | 误差分析 |

|---|---|---|---|

| 单字节写入 | 数据一致(0xAA) | 0xAA | 无误差 |

| 连续区块写入 | 1024字节全部匹配 | 3字节丢失(0x00) | 地址译码信号抖动 |

| 高频测试(20MHz) | 数据稳定 | 偶发错误(0x55→0x54) | 时序保持时间不足 |

实验表明:

- 存储器的基础读写功能在标准频率下表现可靠。

- 高频或低压环境可能导致数据错误,需通过增加等待周期或优化PCB布局解决。

常见问题与解决方案

数据总线冲突

- 现象:读取值始终为0xFF或随机值。

- 原因:总线未正确释放,多设备竞争导致电平冲突。

- 解决:检查片选信号(CE)是否仅在访问时生效,并加入总线缓冲器。

地址偏移错误

- 现象:写入地址0x1000的数据出现在0x1001。

- 原因:地址线连接错位(如A0与A1反接)。

- 解决:重新核对地址线引脚定义。

时序不匹配

- 现象:高速读写时数据丢失。

- 原因:控制器的读写时序未满足存储器tWC(写周期时间)要求。

- 解决:调整控制器的等待状态生成器(Wait State Generator)参数。

实验的工程应用价值

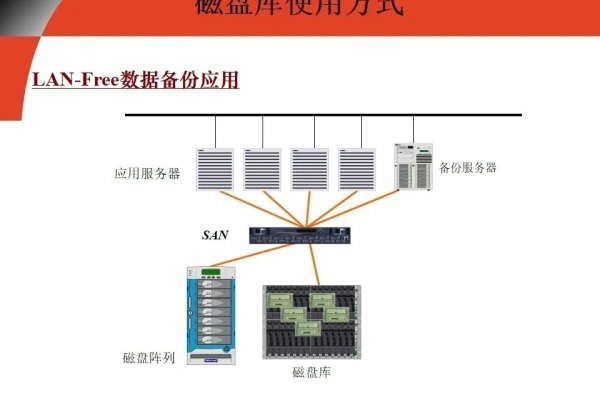

- 嵌入式系统开发:优化存储器访问效率可提升实时系统性能,例如减少DMA传输延迟。

- 硬件调试:通过读写测试定位PCB设计缺陷(如信号完整性不足)。

- 存储技术研究:为新型存储器(如MRAM、ReRAM)的驱动开发提供基准测试方法。

存储器读写实验是硬件开发中的基础却关键的一环,其核心在于时序精准性与信号完整性,实验过程中需结合理论分析(如时序图解读)与工具验证(逻辑分析仪捕获波形),才能高效定位问题,对于开发者而言,掌握存储器操作不仅有助于系统优化,更能为复杂项目(如多核缓存一致性控制)奠定技术基础。

参考文献

- 《计算机组成与设计:硬件/软件接口》David A. Patterson, John L. Hennessy

- IEEE标准《JESD21-C:SRAM器件测试规范》

- STM32F4xx技术参考手册(RM0090)