存储器如何工作?基本原理电路的核心机制是什么?

- 行业动态

- 2025-04-17

- 2

存储器是电子设备中用于保存数据的核心部件,其基本原理电路的设计直接决定了数据的存取速度、稳定性和成本,本文将从半导体存储器的物理结构、工作原理及应用场景三个维度展开分析,帮助读者系统理解存储器技术的关键要点。

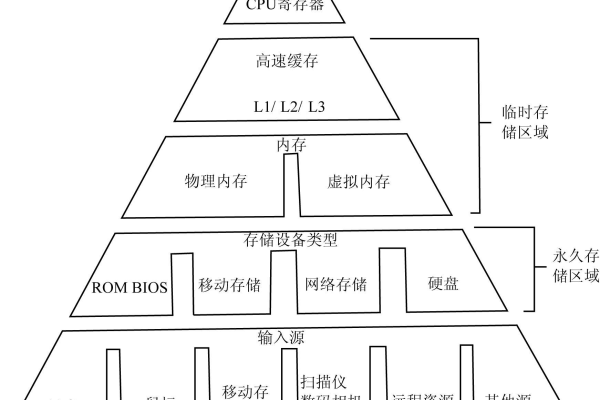

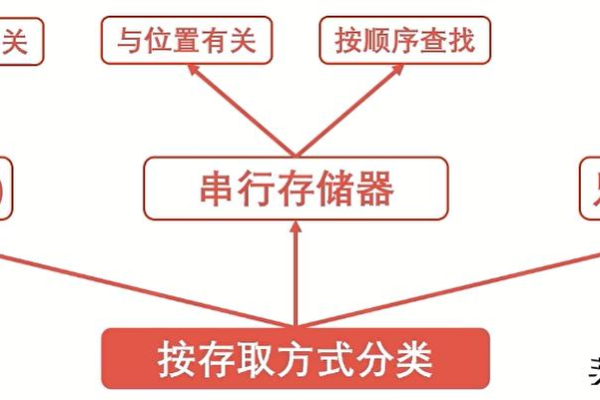

存储器分类与技术特征

现代存储器按数据保持特性可分为易失性存储器(RAM)与非易失性存储器(ROM):

- RAM:数据随断电消失,包含SRAM(静态RAM)和DRAM(动态RAM)

- SRAM通过六晶体管结构(6T Cell)维持数据稳定

- DRAM采用电容+晶体管(1T1C)结构,需定期刷新

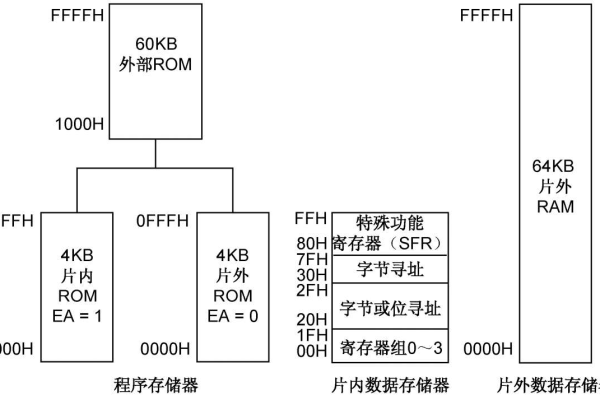

- ROM:数据断电不丢失,包含掩模ROM、PROM、EPROM、EEPROM及Flash

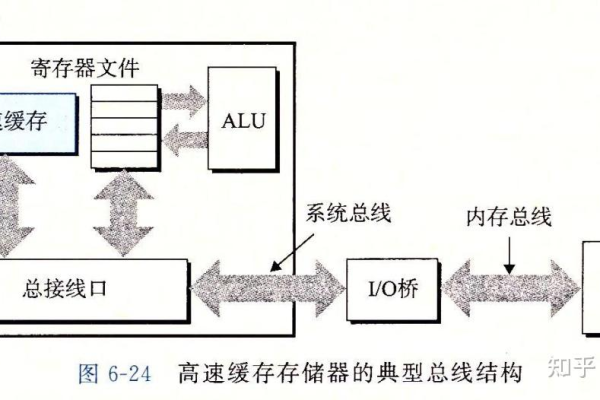

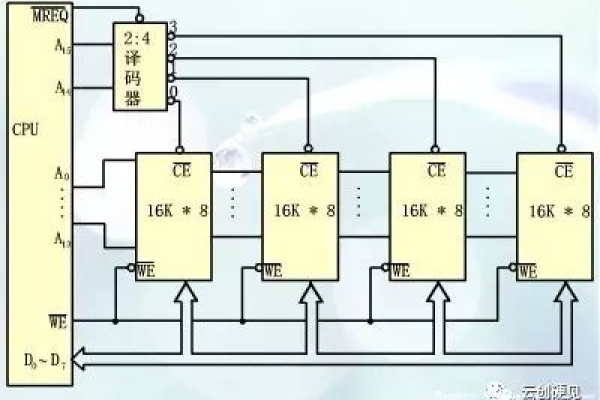

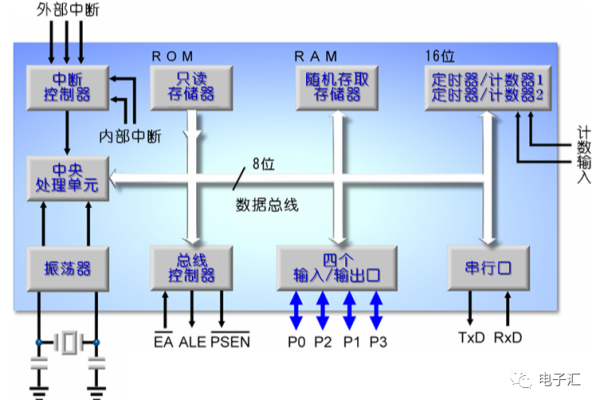

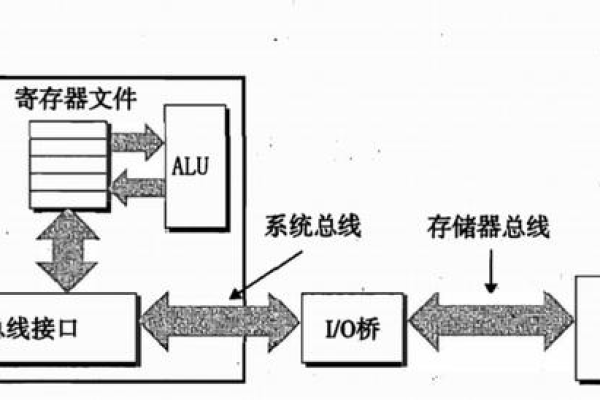

核心电路结构解析

SRAM存储单元

典型六晶体管电路由双CMOS反相器交叉耦合构成(图1),两个存取晶体管受字线控制,当字线(WL)激活时,位线(BL/BLB)通过传输门对存储节点进行读写操作,该结构具有纳秒级访问速度,但单元面积是DRAM的4-6倍。

DRAM存储单元

采用1T1C结构(图2):- 存储晶体管(MOSFET)作为开关

- 存储电容(通常10-30fF)保存电荷

- 数据以电荷形式存储,需每64ms刷新一次

- 读取时通过灵敏放大器检测位线电压变化

NAND Flash存储单元

浮栅MOS晶体管构成(图3):- 编程时向浮栅注入电荷(FN隧穿效应)

- 擦除时移除浮栅电荷

- 通过阈值电压变化区分存储状态

工作过程技术细节

在DRAM的读取周期中,位线预充至VDD/2,字线激活后存储电容与位线形成电荷共享,以某70fF位线电容为例:

ΔV = (Ccell × Vcell) / (Ccell + Cbitline)

= (25fF × 1V) / (25fF + 70fF) ≈ 0.26V

灵敏放大器将该微小电压差放大至全摆幅,完成数据重建。

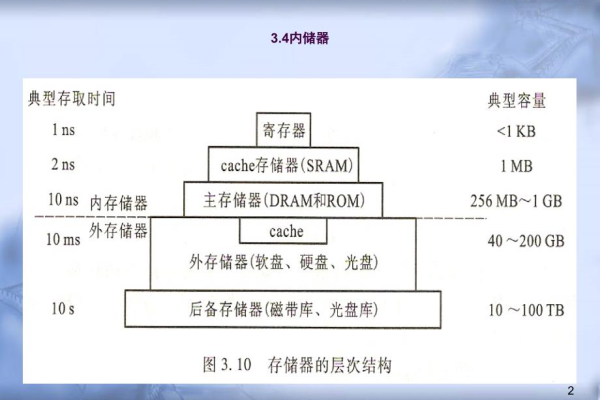

关键参数对比

| 类型 | 访问时间 | 功耗 | 密度 | 典型应用 |

|———|———-|——–|——–|——————|

| SRAM | 1-10ns | 高 | 低 | CPU缓存 |

| DRAM | 10-50ns | 中 | 高 | 主存储器 |

| NAND | 50-100μs | 低 | 极高 | 固态存储 |

演进方向与挑战

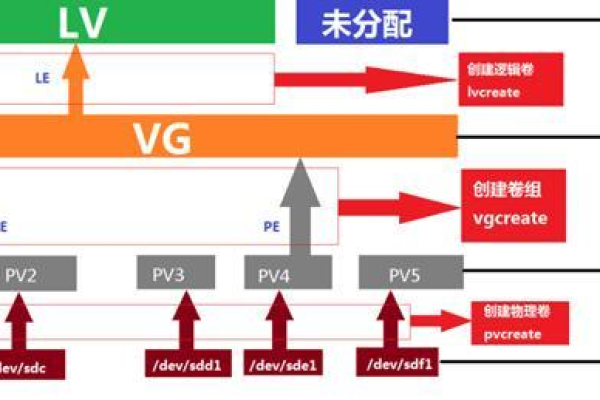

- 3D堆叠技术:三星V-NAND已达236层结构

- 新型存储器:ReRAM/MRAM的研发突破

- 工艺极限:DRAM 1α制程(约12nm)的漏电控制

- 信号完整性:DDR5 6.4Gbps下的时序校准

理解存储器电路原理对芯片设计、系统优化至关重要,随着AI计算需求的爆发,存储器的低延迟访问与高带宽特性正成为下一代计算架构的关键瓶颈,这也推动着新型存储技术的研究与产业化进程。

本文技术论述参考阎石《数字电子技术基础》、Jacob B.《Memory Systems: Cache, DRAM, Disk》以及IEEE固态电路期刊2025年存储技术专刊的研究成果,电路图例依据《CMOS VLSI Design》第四版经典结构绘制。