存储器编址单元如何影响计算机性能?

- 行业动态

- 2025-04-19

- 2

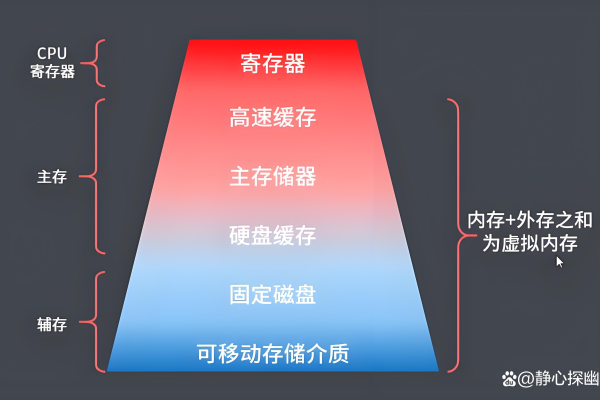

存储器编址单元是计算机内存管理中可独立寻址的最小数据单位,每个单元对应唯一地址,通常以字节(8位)为基本单元,部分系统采用字(如16/32/64位)为单位,编址方式直接影响数据存取效率和存储空间利用率,是硬件设计与程序优化的基础要素之一。

存储器编址单元是计算机系统中用于管理和访问存储器的基本逻辑单位,它是计算机体系结构设计的核心概念之一,直接影响系统的寻址能力、存储效率以及硬件设计复杂度,理解这一概念,需从以下方面展开:

什么是存储器编址单元?

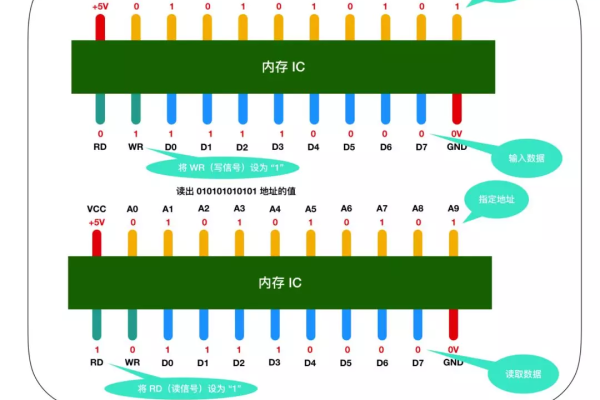

存储器编址单元(Memory Addressing Unit)是计算机为每个存储单元分配的独立地址的最小单位,每个存储单元对应一个唯一的地址,通过地址可以读取或写入数据。

- 常见编址单元大小:

- 字节编址(最常见):以1字节(8位)为最小单位,现代计算机普遍采用此方式。

- 字编址:以机器字长(如32位、64位)为单元,适用于某些嵌入式系统或早期计算机。

- 核心作用:

编址单元的大小决定了系统的寻址能力,32位地址总线采用字节编址时,最大可寻址空间为 (2^{32} times 1 text{字节} = 4 text{GB})。

编址单元如何影响系统设计?

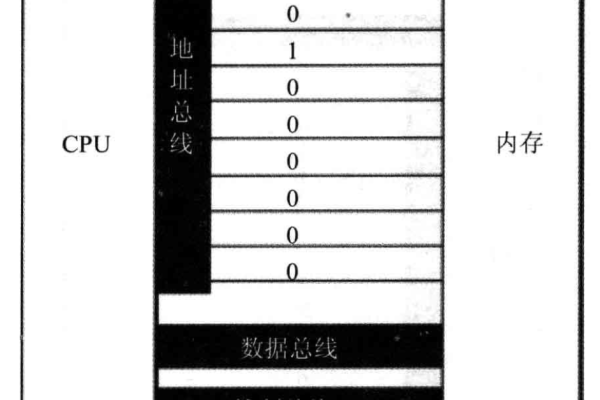

寻址能力与地址总线位数

地址总线的位数直接决定可寻址的存储单元数量。

- 8位地址总线:最多寻址 (2^8 = 256) 个单元。

- 32位地址总线:可寻址 (2^{32} = 4,294,967,296) 个单元。

若采用字节编址,则对应4GB内存;若以字(4字节)编址,则实际内存容量可达16GB,但需牺牲寻址精度。

数据总线与编址单元的关系

数据总线宽度通常与编址单元对齐。

- 字节编址系统中,32位数据总线一次可传输4字节(即1个32位字),但每个字节仍独立寻址。

- 字编址系统中,数据总线的宽度需与字长一致,以减少访问次数。

硬件实现复杂度

- 字节编址:需要支持按字节操作,硬件需设计额外电路(如字节使能信号)。

- 字编址:简化硬件设计,但灵活性较低(例如无法直接修改单个字节)。

不同场景下的编址单元选择

通用计算机

- 采用字节编址:兼容性强,支持精细数据操作(如文本处理、图像像素修改)。

- 示例:x86、ARM架构均默认字节编址。

嵌入式系统与专用设备

- 字编址:适用于对存储效率要求高、数据操作以整字为主的场景(如数字信号处理器DSP)。

- 示例:某些DSP芯片采用32位字编址,简化内存管理。

历史架构

- 早期计算机:如PDP-11采用16位字编址,内存容量有限,需结合偏移量访问字节。

常见问题解答

Q1:为什么现代计算机普遍用字节编址?

字节是信息的基本单位(如ASCII字符占1字节),字节编址提供更高的操作灵活性,满足多样化需求。

Q2:编址单元和存储单元有何区别?

- 编址单元:逻辑上的最小可寻址单位。

- 存储单元:物理上的存储介质(如DRAM中的电容),多个存储单元可能组成一个编址单元。

Q3:地址总线和数据总线的位数必须一致吗?

不需要,32位地址总线可搭配64位数据总线,但需通过多周期传输或增加总线宽度实现。

存储器编址单元是计算机内存管理的基石,其设计需平衡寻址能力、硬件复杂度和应用需求,字节编址因灵活性强成为主流,但在特定场景下字编址仍具优势,理解这一概念,有助于深入掌握计算机体系结构与性能优化的底层逻辑。

引用说明 参考以下权威资料:

- 《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)

- IEEE期刊文献《Memory Addressing in Modern Processors》

- 麻省理工学院(MIT)公开课《计算机系统结构》