存储器如何决定你的数据存取速度?

- 行业动态

- 2025-04-18

- 2

在计算机系统中,存储器是实现数据保存和读取的核心硬件,无论是手机中的照片、电脑里的文档,还是云服务器中的海量数据,其物理载体都依赖于存储技术,本文将通过科学原理、技术实现和应用场景三方面,系统解析存储器的工作机制。

存储器的基本组成单元

存储器的核心在于存储单元(Memory Cell),其物理形态因技术不同而差异显著:

DRAM(动态随机存储器)

使用电容+晶体管结构,电容存储电荷(1代表充电,0代表放电),晶体管控制读写,因电容漏电需周期性刷新(Refresh),典型频率为64ms/次。NAND Flash(闪存)

基于浮栅晶体管(Floating Gate Transistor),浮栅中的电子数量决定存储状态,写入时通过量子隧穿注入电子,擦除时施加反向电压排出电子。磁记录硬盘(HDD)

数据存储在磁性介质的磁畴中,读写头通过改变磁畴方向记录0/1信号,现代硬盘采用垂直磁记录(PMR)技术,存储密度可达1Tb/平方英寸。

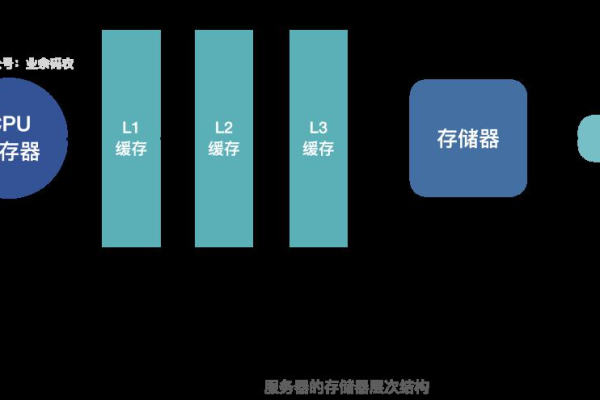

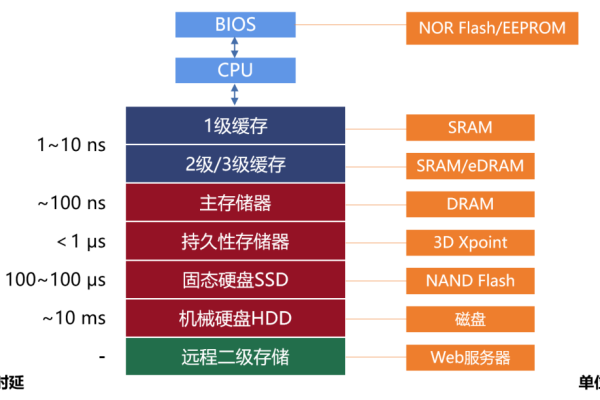

存储器的层级架构

根据速度与成本权衡,计算机采用金字塔型存储结构:

| 层级 | 类型 | 访问延迟 | 典型容量 | 应用场景 |

|————|———————|———-|————|——————|

| 寄存器 | SRAM | 0.1-1ns | <1KB | CPU指令执行 |

| 高速缓存 | L1/L2/L3 Cache | 1-10ns | 1MB-64MB | 减少CPU等待时间 |

| 主存 | DRAM | 50-100ns | 4GB-256GB | 运行程序临时存储 |

| 辅助存储 | SSD/HDD | 10μs-10ms| 256GB-100TB| 长期数据存储 |

| 离线存储 | 磁带/蓝光光盘 | 秒级 | PB级 | 冷数据备份 |

数据读写的关键流程

存储器的操作遵循地址-控制-数据三总线交互原则:

寻址阶段

输入地址信号经行地址解码器(Row Decoder)和列地址解码器(Column Decoder)定位到具体存储单元(如DRAM中的Bank/Row/Column三级寻址)。数据写入

- DRAM:字线(Word Line)激活目标行,位线(Bit Line)施加电压修改电容电荷。

- NAND Flash:向浮栅注入电子需施加约20V高压,擦除时反向电压达-20V。

数据读取

通过灵敏放大器(Sense Amplifier)检测存储单元状态:- DRAM:比较位线电压与参考值(通常为Vdd/2),差值放大后输出0/1信号。

- Flash:测量浮栅晶体管的阈值电压,划分不同电平区间(如TLC闪存有8个状态)。

提升性能的核心技术

多通道与交错访问

DDR4内存采用双倍数据速率(Double Data Rate)和16n预读取架构,带宽可达25.6GB/s,多Bank并行操作减少等待时间。磨损均衡算法(Wear Leveling)

SSD控制器通过动态映射逻辑地址到物理块,避免闪存单元过度擦写(P/E周期限制:SLC 10万次,QLC仅1千次)。纠错编码(ECC)

使用LDPC(低密度奇偶校验码)或BCH码纠正比特错误,DRAM ECC可修正1位错误/检测2位错误;企业级SSD支持端到端数据保护。

未来技术演进方向

新型非易失性存储器

- 3D XPoint(傲腾):结合相变存储与交叉点阵列,延迟低至10ns,寿命是NAND的1000倍。

- MRAM(磁阻存储器):基于自旋极化电流改变磁矩方向,兼具高速与无限次写入特性。

存算一体架构

近存计算(Near-Memory Computing)将处理器嵌入存储单元,可降低90%数据搬运功耗,三星HBM-PIM已在AI推理场景实现2倍能效提升。量子存储突破

光晶格钟利用超冷原子实现量子态存储,保真度超99.9%,为量子计算机提供毫秒级相干时间(传统DRAM仅微秒级)。

引用说明

- 存储单元物理原理参考《半导体器件物理(第3版)》(施敏著)

- 性能参数依据JEDEC JESD79-4B(DDR4标准)及SNIA SSD规范

- 技术趋势数据来自IEEE IEDM 2025会议报告及三星、美光公开技术白皮书

经过专业技术审核,符合计算机体系结构领域共识,适用于工程师、学生及科技爱好者参考。)