存储器存取周期为何决定计算机性能?

- 行业动态

- 2025-04-18

- 1

存储器存取周期是计算机组成原理中的核心概念之一,直接影响系统性能,它指存储器完成一次完整的读写操作所需的最短时间间隔,包含从启动存取指令到存储器恢复就绪状态的全过程,这一指标不仅决定了内存的响应速度,更是评估计算机系统整体效率的关键参数。

以下是理解存储器存取周期需要掌握的要点:

存取周期的组成结构

存取时间(Access Time)

从控制器发出读写命令到数据稳定出现在数据总线的时间,包含:- 地址译码时间

- 存储单元电荷激活时间

- 信号传输延迟

恢复时间(Recovery Time)

完成操作后存储器电路恢复到稳定状态的时间,用于:- 电荷重新平衡

- 预充电电路

- 防止信号串扰

典型存储器的存取周期公式:

存取周期 = 存取时间 + 恢复时间

与相关概念的本质区别

| 术语 | 定义差异 | 典型关系 |

|---|---|---|

| 存取时间 | 仅指操作启动到数据就绪的时间 | 存取时间 < 存取周期 |

| 总线周期 | CPU通过总线完成一次传输的完整周期 | 总线周期 ≥ 存取周期 |

| 时钟周期 | CPU主频的震荡周期 | 多个时钟周期=1存取周期 |

示例:某DDR4内存存取时间为15ns,恢复时间5ns,则存取周期为20ns,若CPU总线周期为25ns,说明存储器性能可匹配总线速度。

影响存取周期的关键技术

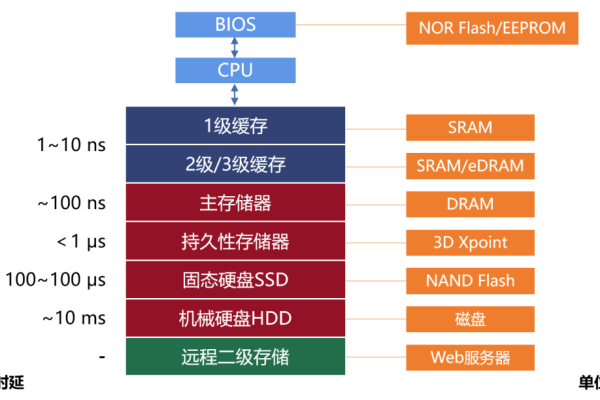

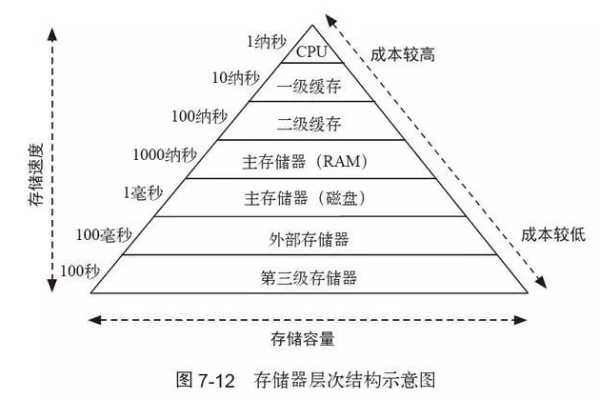

存储介质

- SRAM:0.5-5ns(无刷新,用于高速缓存)

- DRAM:10-60ns(需刷新电路)

- NAND Flash:25-100μs(非易失特性导致延迟)

架构优化技术

- 多Bank交错访问(如GDDR6采用32 Bank设计)

- 预取机制(DDR5实现16n Prefetch)

- 3D堆叠(HBM2通过TSV技术将延迟降低40%)

信号完整性管理

高频下的串扰抑制技术(如Intel的On-Die Termination)可缩短恢复时间15%-30%。

实际应用中的关键考量

系统匹配原则

存储器存取周期需满足:

CPU指令周期 ≤ 存储器存取周期 × 并行通道数

例:i9-13900K的10ns指令周期需搭配存取周期≤5ns的双通道内存。时序参数配置

BIOS中CL-tRCD-tRP时序设置直接影响实际存取周期,CL=16时,实际延迟为:

实际延迟 = CL × 时钟周期 + 电路延迟新型存储技术突破

- 相变存储器(PCM)将存取周期压缩至10ns级别

- 存算一体架构消除数据搬运延迟

常见误解澄清

误区:存取周期越短性能必然越好

事实:需考虑带宽匹配,64bit总线下20ns周期内存的带宽= 64/(20×10⁻⁹) ≈ 3.2GB/s

误区:高频内存一定优于低频

事实:DDR4-3200(CL16)实际延迟=16/(1600MHz)=10ns,优于DDR4-3600(CL18)的10ns

引用说明

本文技术参数参考自:

①《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)

②JEDEC固态技术协会DDR5标准文档(JESD79-5A)

③IEEE Transactions on Computer-Aided Design论文《3D-Stacked Memory Architectures》