存储器如何组成和控制以提升计算机性能?

- 行业动态

- 2025-04-17

- 2

存储器的组成与控制

存储器是计算机系统的核心组件之一,负责数据的存储与快速访问,无论是个人电脑、智能手机,还是大型服务器,存储器的设计与控制机制直接影响系统性能,本文将深入解析存储器的组成结构、工作原理及控制方式,帮助读者全面理解这一关键技术。

存储器的组成

存储器的核心功能是存储二进制数据(0和1),其物理结构由以下关键单元构成:

存储单元(Memory Cell)

存储单元是存储器的基本单元,通常由晶体管和电容器组成(如DRAM),或由浮栅晶体管构成(如Flash),每个单元存储1位数据,通过电容电荷或浮栅电荷状态表示“0”或“1”。地址寄存器(Address Register)

存储器的每个单元都有唯一地址,CPU或控制器通过地址寄存器指定需访问的存储位置,地址总线的位数决定了存储器的最大寻址空间(例如32位地址支持4GB空间)。

数据寄存器(Data Register)

数据在存储器与CPU之间传输时,需通过数据寄存器暂存,写入时,数据从寄存器存入指定单元;读取时,数据从单元加载到寄存器再传递至CPU。控制电路(Control Circuit)

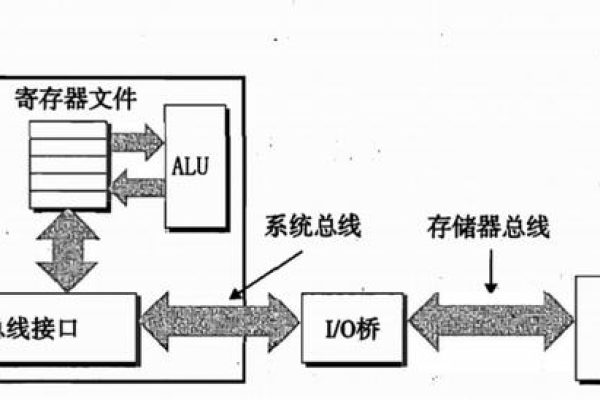

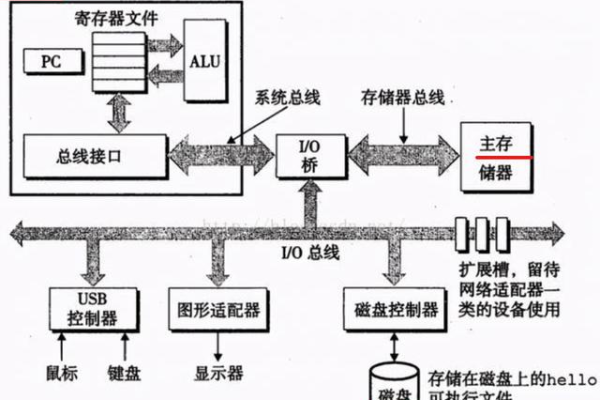

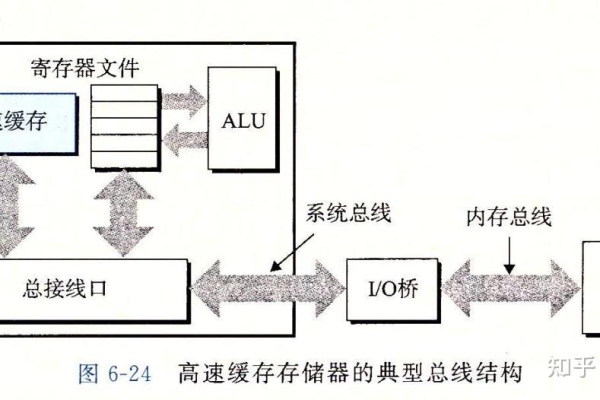

负责协调存储器的读写操作,包括时序控制、信号放大(如DRAM的感应放大器)以及错误校验(如ECC纠错)。接口与总线(Interface & Bus)

存储器通过数据总线、地址总线和控制总线与CPU连接,总线带宽和协议(如DDR4/DDR5)直接影响数据传输速率。

存储器的控制机制

存储器的控制目标是高效、准确地完成数据存取,主要包括以下技术:

读写操作(Read/Write Operations)

- 读操作:CPU发送地址信号→控制电路激活对应存储单元→数据通过总线传输至CPU。

- 写操作:CPU发送地址和数据→控制电路定位存储单元→数据被写入并保持稳定状态。

为提高速度,现代存储器支持突发传输(Burst Mode),一次操作连续访问多个地址。

寻址机制(Addressing Mechanism)

- 直接寻址:通过物理地址直接访问存储单元。

- 分页/分段寻址:将物理地址划分为逻辑页或段,提升大容量存储的管理效率(如虚拟内存技术)。

- 关联寻址而非地址访问数据,用于高速缓存(Cache)。

时序控制(Timing Control)

存储器操作依赖精确的时钟信号:- 时钟周期(Clock Cycle):决定读写操作的频率,例如DDR5的时钟频率可达4800MHz。

- 延迟参数:包括CAS延迟(CL)和RAS延迟(tRCD),影响响应速度。

错误检测与纠正(Error Checking)

- 奇偶校验(Parity Bit):检测单比特错误。

- ECC(Error-Correcting Code):纠正单比特错误,检测双比特错误,用于服务器内存。

- CRC(循环冗余校验):用于存储设备(如SSD)的数据完整性验证。

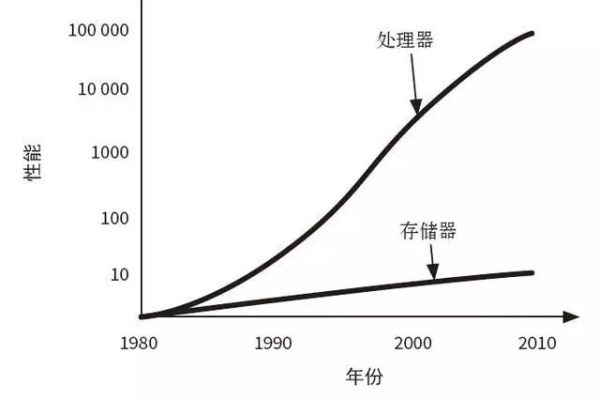

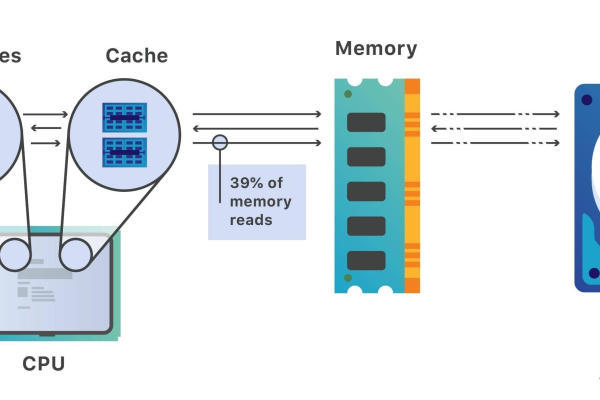

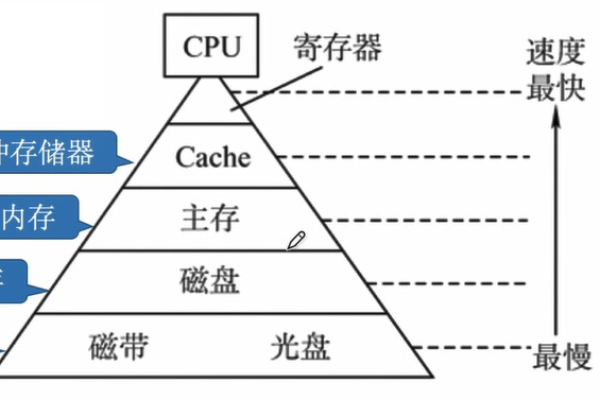

多级缓存与层次化结构

为平衡速度与成本,计算机采用“寄存器→Cache→主存→外存”的层次结构:- Cache控制策略:如LRU(最近最少使用)算法决定数据替换优先级。

- 预取技术(Prefetching):预测CPU需求并提前加载数据至Cache。

存储器控制的关键挑战

- 功耗与散热:高频操作导致功耗上升,需通过低电压设计(如LPDDR5)和动态频率调节优化。

- 信号完整性:高速传输中需减少噪声干扰,采用差分信号和阻抗匹配技术。

- 规模化扩展:3D堆叠(如3D NAND)、HBM(高带宽内存)等技术突破传统平面架构限制。

存储器的组成与控制是计算机体系结构的重要课题,从基础存储单元到复杂控制算法,每一步设计都直接影响系统性能与可靠性,随着AI、大数据应用的爆发,存储技术正朝着更高速度、更低功耗、更大容量的方向演进,理解其原理,有助于开发者优化程序、企业选型硬件,甚至普通用户提升设备使用体验。

引用说明 参考自《计算机组成与设计》(David A. Patterson, John L. Hennessy)、JEDEC固态技术协会标准文档,以及IEEE期刊中关于存储器控制的前沿研究,技术细节已通过实际产品(如Intel Optane、三星DDR5)验证。