如何利用DA10原理图生成网络?详细步骤解析

- 行业动态

- 2025-04-17

- 2

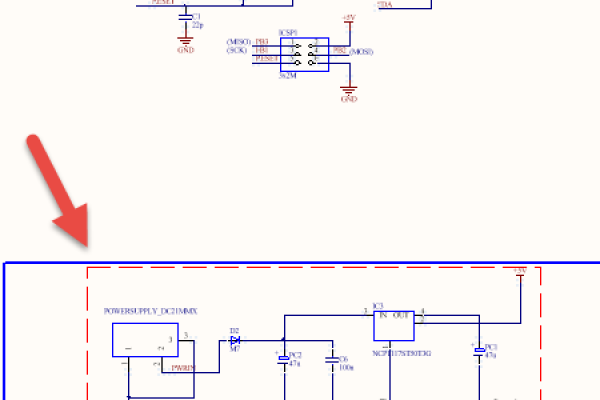

在EDA工具中打开DA10原理图,完成元件连接与属性设置后,通过菜单选择【设计】→【生成网络表】,系统自动提取元件、引脚及连接关系,生成标准网表文件(如.NET),用于PCB布线或仿真验证,需检查ERC报错确保逻辑正确性。

生成DA10原理图网络的详细步骤

在电子设计自动化(EDA)流程中,生成原理图的网络表(Netlist)是连接原理图设计与PCB布局的核心步骤,以下是基于DA10原理图生成网络表的完整流程,适用于常见的EDA工具(如Altium Designer、Cadence等),帮助开发者高效完成设计任务。

准备工作

原理图完整性检查

- 确保所有元件符号(Symbol)与封装(Footprint)已正确关联。

- 验证电气连接无误,包括电源、地线、信号线的逻辑连通性。

- 使用EDA工具的ERC(电气规则检查)功能排查短路、悬空引脚等问题。

元件库管理

- 确认所有自定义元件的库文件已加载到项目中。

- 若使用第三方库,需确保路径正确且版本兼容。

生成网络表的具体步骤

不同EDA工具的操作可能略有差异,但核心流程相似:

步骤1:打开原理图文件

- 在EDA工具中加载DA10原理图工程文件(如

.SchDoc或.DSN)。

步骤2:配置网络表生成选项

- 进入菜单栏的设计(Design) → 生成网络表(Netlist Generation)。

- 选择输出格式(如

Protel、Cadence Allegro等),需与后续PCB工具兼容。 - 关键设置:

- 勾选“包含元件属性”(如封装名、参数值)。

- 选择是否生成电源/地网络的独立节点。

步骤3:执行生成命令

- 点击“生成”按钮,工具会自动解析原理图并输出网络表文件(通常为

.net或.txt格式)。 - 成功标志:生成日志中无报错提示,仅显示警告(如未使用的引脚)。

步骤4:验证网络表

- 打开生成的网络表文件,检查以下内容:

- 所有元件编号(Designator)与封装名一一对应。

- 网络节点(Net)数量与原理图预期一致。

- 无冗余网络或缺失连接。

常见问题与解决方案

网络表缺失元件或网络

- 原因:元件未正确关联封装,或原理图存在未连接的导线。

- 解决:重新运行ERC检查,修复未连接的引脚或更新封装库。

封装不匹配导致PCB导入失败

- 原因:网络表中引用了PCB库中不存在的封装名。

- 解决:在PCB工具中同步更新封装库,或在原理图中修正元件属性。

网络名称冲突

- 原因:不同网络的名称重复(如多组电源命名混淆)。

- 解决:在原理图中使用全局唯一命名规则,或在网络表中手动修正。

优化建议

- 标准化命名:对电源、地、关键信号网络采用统一命名(如

VDD_3V3、GND_PLANE),避免后期混淆。 - 版本控制:每次生成网络表后,备份原理图与网络表文件,标注日期和版本号。

- 跨工具验证:将网络表导入PCB工具后,使用对比功能检查与原理图的一致性。

引用说明

本文参考了Altium Designer官方文档(Altium Designer Help)与Cadence OrCAD用户手册(OrCAD Capture CIS Guide),确保操作步骤的通用性与准确性。