存储器电路如何工作?

- 行业动态

- 2025-04-17

- 2

存储器电路通过存储单元阵列保存二进制数据,每个单元由晶体管与电容/触发器构成,利用电荷或双稳态结构存储0/1信号,地址译码器定位目标单元,读写控制电路根据指令操作数据:写入时施加电压改变电荷状态,读取时检测电平并放大输出,静态存储器(SRAM)通过双稳态电路保持数据,动态存储器(DRAM)依赖电容电荷需定期刷新。

存储器是计算机系统中用于保存数据和指令的核心组件,无论是手机、电脑还是云端服务器,所有电子设备都依赖存储器实现信息的高速存取,本文将深入解析存储器电路如何通过微观电子结构实现数据的存储与读取,帮助读者理解这一现代科技的基础原理。

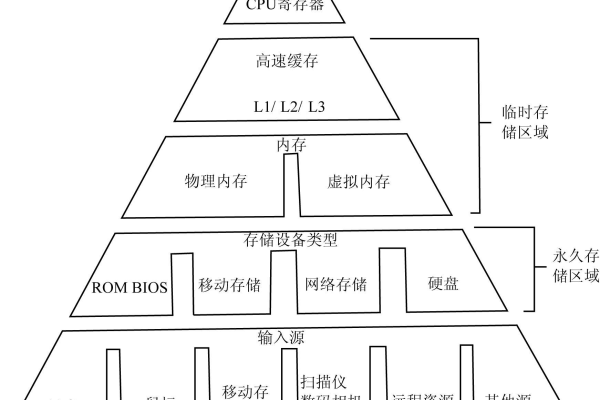

存储器基本构成

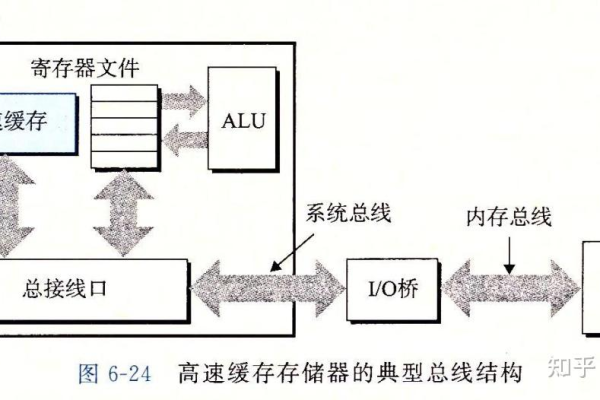

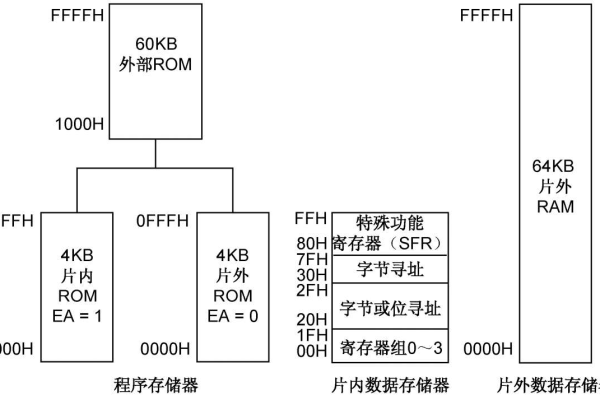

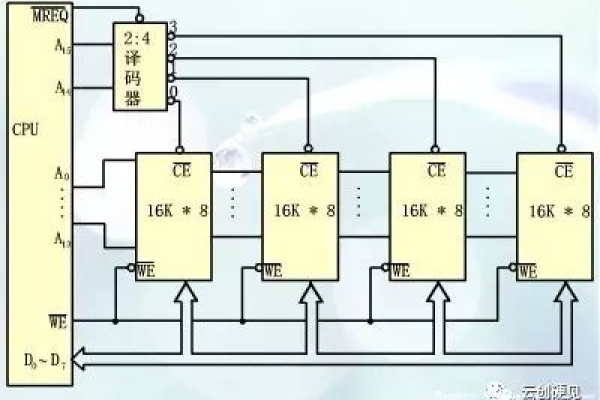

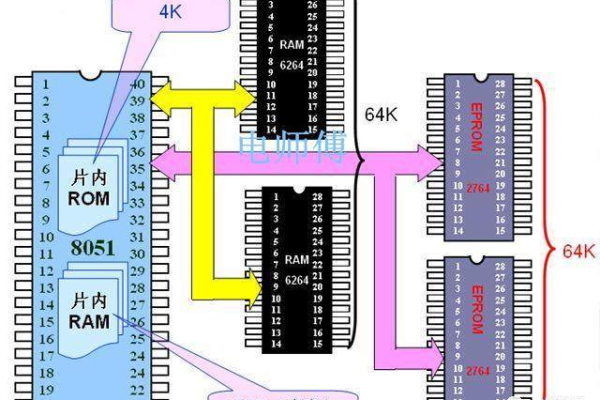

存储器电路由存储单元阵列、地址译码器、读写控制电路三大部分组成:

- 存储单元:每个单元存储1位二进制数据(0或1),由晶体管与电容等元件构成

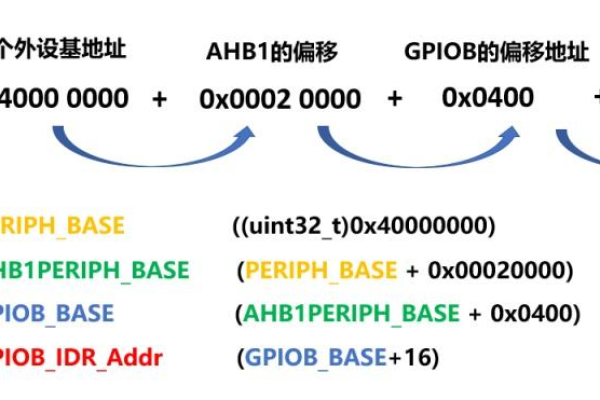

- 地址译码器:将二进制地址转换为物理存储位置的坐标选择信号

- 控制电路:协调读写时序,包含灵敏放大器(Sense Amplifier)等关键组件

核心工作原理

- 写入过程

当CPU发出写指令时:

- 地址总线传送目标位置(如00101101)

- 译码器激活对应存储单元的行列线

- 驱动电路施加特定电压(DRAM约1.2-3.3V)

- 存储单元的电容器充电(存1)或放电(存0)

- 读取过程

读取操作时:

- 字线(Word Line)电压提升至导通阈值

- 位线(Bit Line)连接灵敏放大器

- 电荷变化被放大1000倍以上(典型值)

- 比较器将模拟信号转换为数字信号输出

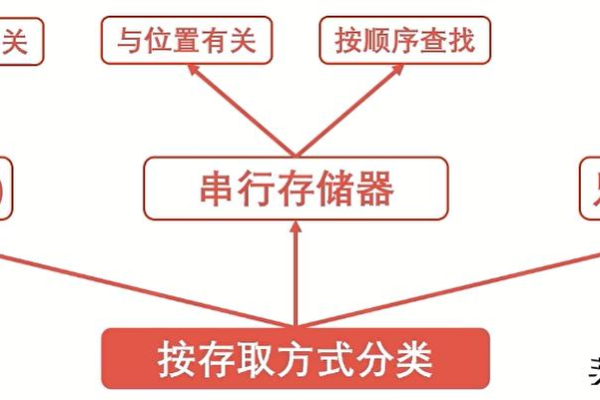

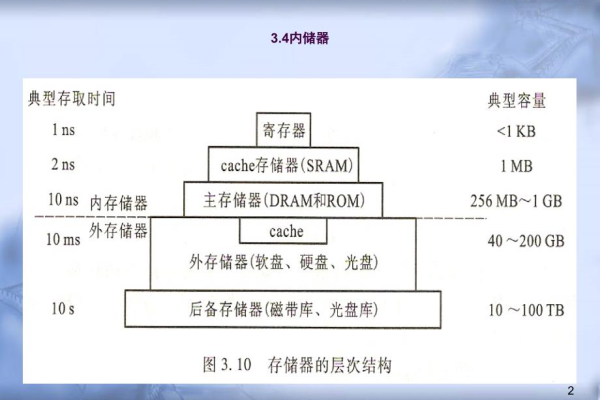

不同类型存储器特性对比

| 类型 | 存储介质 | 刷新周期 | 存取速度 | 典型容量 | 功耗 |

|————|————|———-|———-|———-|——–|

| DRAM | 电容电荷 | 64ms | 50-100ns | 4-64GB | 中 |

| SRAM | 触发器状态 | 无需刷新 | 0.5-5ns | 1-32MB | 高 |

| NAND闪存 | 浮栅电荷 | 无需刷新 | 25-100μs | 256GB-8TB| 低 |

| PCM | 相变材料 | 无需刷新 | 50-100ns | 实验阶段 | 中低 |

关键技术解析

- DRAM刷新机制

电容器存在漏电流(典型值约0.1fA),需每64ms执行:

- 行地址计数器遍历所有行

- 灵敏放大器重新写入衰减的电荷

- 消耗约5-10%的总带宽

- 3D NAND堆叠技术

现代闪存采用垂直堆叠结构:

- 层数从32层(2014)发展到232层(2022)

- 单元尺寸缩小至15nm以下

- 采用电荷陷阱(Charge Trap)替代浮栅结构

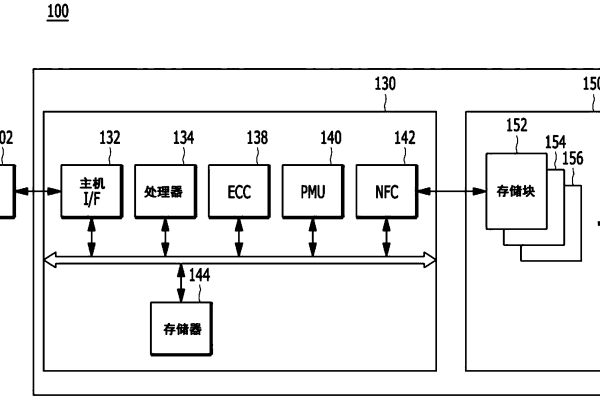

- 纠错编码(ECC)

每512字节数据附加6-8字节校验码:

- 可纠正1-8位随机错误

- 检测多比特突发错误

- 采用BCH或LDPC算法

存储器电路发展前沿

- 新型存储介质

- 阻变存储器(RRAM):利用金属氧化物阻值变化

- 磁阻存储器(MRAM):基于电子自旋方向存储

- 铁电存储器(FeRAM):利用铁电材料极化特性

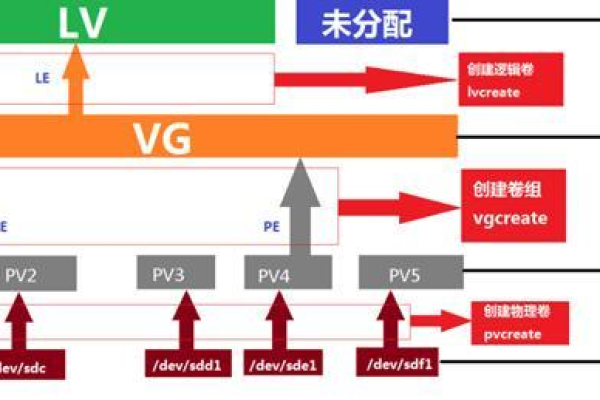

- 存算一体技术

通过在存储阵列内集成计算单元:

- 减少数据搬运能耗(占比可达90%)

- 支持矩阵乘加运算加速

- 适用于AI推理场景

- 近存计算架构

采用2.5D/3D封装技术:

- 将处理器与HBM显存集成

- 带宽提升至460GB/s(HBM3)

- 延迟降低至传统架构的1/5

实际应用场景

- 手机LPDDR5内存:采用Bank Group架构,速率可达6400Mbps

- 企业级SSD:配备DRAM缓存+超薄介电层(<10nm)

- 车规级存储器:满足-40℃~125℃工作温度,抗振强度>20G

存储器电路的技术演进直接推动着信息革命进程,从1947年威廉姆斯管的1位存储,到如今单颗芯片可存储1Tb数据,存储密度每18个月翻倍的规律仍在延续,理解这些精密电路的工作原理,有助于我们更好把握未来计算体系的发展方向。

引用说明:

[1] IEEE固态电路期刊(2025存储技术专刊)

[2] 美光科技《3D NAND架构白皮书》

[3] JEDEC DDR5标准规范(JESD79-5B)

[4] 清华大学《新型存储器技术研究进展》