存储器的核心组成部件究竟有哪些?

- 行业动态

- 2025-04-17

- 2

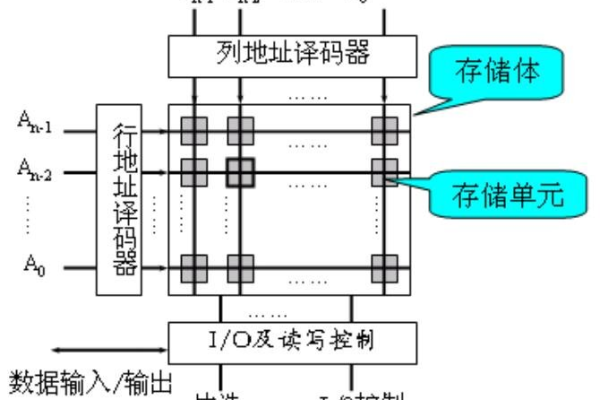

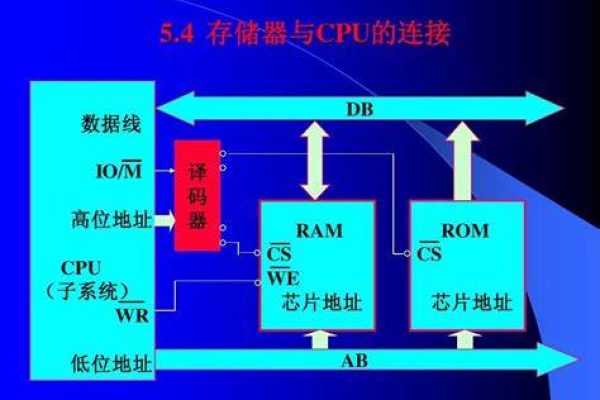

存储器主要由存储体、地址寄存器、数据寄存器和控制电路组成,存储体用于存储二进制数据,地址寄存器定位数据位置,数据寄存器暂存读写信息,控制电路协调操作时序,按功能分为主存(RAM、ROM)和辅存(硬盘、SSD),按速度层次包含高速缓存、内存和外存,通过总线与CPU交互实现数据存取。

在数字设备中,存储器是核心部件之一,负责数据的存储与调用,其组成结构直接影响设备的性能、响应速度和数据安全性,以下从技术角度详细解析存储器的组成及其工作原理。

存储器的核心组成

现代计算机系统的存储器通常分为内部存储器和外部存储器两类,两者协同工作以满足不同场景的数据访问需求。

内部存储器(主存)

内部存储器直接与CPU交互,具有高读写速度但容量有限,主要包括以下类型:

随机存取存储器(RAM)

- DRAM(动态RAM):通过电容存储电荷表示数据,需定期刷新,成本低且密度高,广泛用于计算机内存条。

- SRAM(静态RAM):基于触发器电路,无需刷新,速度更快但成本高昂,多用于CPU高速缓存(如L1、L2缓存)。

只读存储器(ROM)

- PROM(可编程ROM):出厂后仅允许一次编程,用于存储固化程序。

- EPROM(可擦写PROM):通过紫外线擦除数据,支持多次编程。

- EEPROM(电擦写PROM):通过电压擦除,常用于保存BIOS配置。

外部存储器(辅存)

外部存储器用于长期保存数据,容量大但速度较慢,常见类型包括:

- 硬盘驱动器(HDD)

由磁性盘片、机械臂和读写头组成,通过磁化颗粒方向记录数据,容量可达数十TB。

- 固态硬盘(SSD)

基于NAND闪存芯片,无机械部件,依赖浮栅晶体管存储电荷,读写速度比HDD快10倍以上。

- 光盘(CD/DVD/Blu-ray)

利用激光在反射层刻录凹坑记录数据,成本低但易受物理损坏。

- U盘与存储卡

使用NAND闪存技术,通过USB或SD接口连接设备,便携性强。

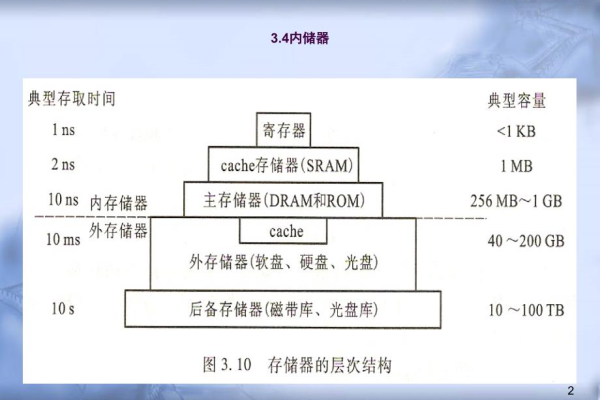

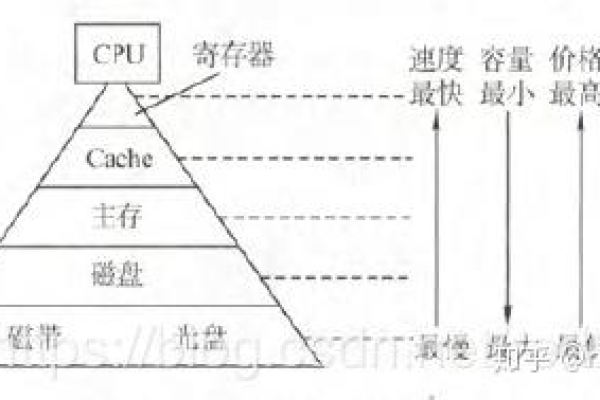

存储器的分层架构

为平衡速度、容量与成本,计算机系统采用多级存储体系:

- 寄存器:CPU内部极小容量存储器,直接参与运算(纳秒级延迟)。

- 高速缓存(Cache):分为L1、L2、L3三级,缓存频繁访问的数据,减少CPU等待时间。

- 主存(RAM):运行中的程序与数据暂存区,断电后数据丢失。

- 辅存(HDD/SSD):长期存储操作系统、应用与用户文件。

(注:示意图仅为示例,实际结构因设备而异)

关键技术支撑

存储单元结构

- DRAM单元:由1个晶体管+1个电容构成,电容电荷状态表示0/1。

- NAND闪存:采用浮栅晶体管,通过电子隧穿效应写入数据,支持多层堆叠(如3D NAND)。

接口与协议

- 内存接口:DDR4/DDR5标准提升带宽与能效。

- 存储协议:NVMe协议优化SSD的PCIe通道利用率,降低延迟。

纠错与寿命管理

- ECC(纠错码):检测并修复内存中的单比特错误。

- 磨损均衡:SSD通过算法平均分配写入次数,延长寿命。

未来发展趋势

新型存储技术

- 3D XPoint:英特尔与美光联合研发,速度接近DRAM,容量媲美NAND。

- MRAM(磁阻RAM):非易失性,抗辐射,适合物联网设备。

容量与密度提升

- QLC NAND:单单元存储4比特数据,成本下降但写入寿命缩短。

- 3D堆叠技术:通过垂直堆叠芯片突破平面工艺限制。

智能化存储

结合AI算法预测数据访问模式,动态优化缓存策略。

引用说明

本文参考以下权威资料:

- 《计算机组成与设计:硬件/软件接口》David A. Patterson, John L. Hennessy

- JEDEC固态技术协会公开标准(JESD79-4B DDR4 SDRAM)

- 西部数据公司《3D NAND技术白皮书》

- 英特尔《Optane技术架构解析》