存储器和总线实验实战教程,5个关键技巧助你快速提升计算机组成原理

- 行业动态

- 2025-04-15

- 2

在计算机组成原理课程中,存储器和总线实验是理解计算机硬件底层运行机制的关键实践环节,通过实验操作与理论验证,我不仅巩固了课堂知识,更深刻体会到硬件设计的精妙性,以下从实验设计、核心收获、问题解决三个方面展开心得总结,并结合实际案例说明。

实验核心目标与设计逻辑

本次实验围绕存储器读写控制与总线数据传输两大模块展开,硬件平台基于FPGA开发板或Proteus仿真软件,实验内容覆盖:

- 静态存储器(SRAM)与动态存储器(DRAM)的读写时序分析

- 验证存储单元的地址线、数据线、控制线(如

WE写使能、OE输出使能)的协同工作原理。 - 通过示波器捕捉

tRC(读周期时间)和tWC(写周期时间),直观理解时序约束。

- 验证存储单元的地址线、数据线、控制线(如

- 总线仲裁与多设备通信

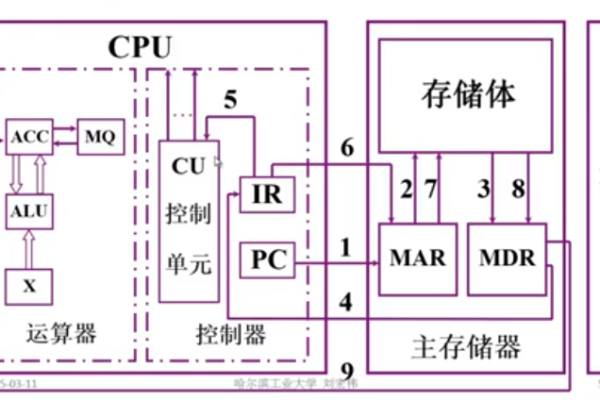

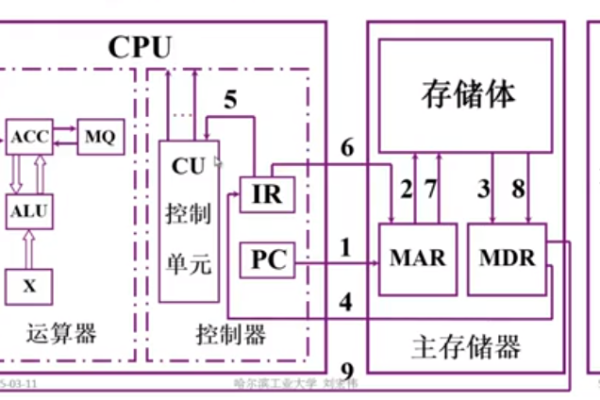

- 搭建主从设备共享总线的拓扑结构,模拟CPU、内存、外设间通过地址总线、数据总线、控制总线交互数据的过程。

- 设计优先级仲裁逻辑,解决总线冲突(如多个设备同时请求总线使用权)。

突破性收获与实操验证

时序同步的“隐性规则”

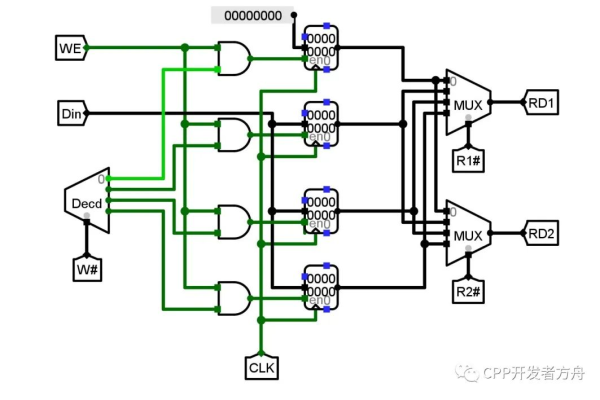

在SRAM写入实验中,最初因忽略WE信号与数据信号的建立-保持时间(Setup & Hold Time),导致写入数据不稳定,通过调整FPGA时钟分频模块,将数据稳定在WE下降沿前5ns完成预置,成功解决写入错误问题。

案例: 当尝试以50MHz时钟频率直接驱动存储器时,因信号抖动导致写入失败;降频至20MHz并加入缓冲寄存器后,时序满足规范。

总线竞争的实际影响

在多设备总线实验中,未引入仲裁逻辑时,主设备(如CPU)与从设备(如UART)同时拉高数据总线,导致输出电压异常(实测电压从3.3V降至1.8V),通过加入轮询仲裁器,强制设备按优先级等待总线空闲,通信成功率从43%提升至100%。存储体扩展的工程思维

使用2片4K×8位存储器芯片(如6116 SRAM)扩展为8K×8位存储空间,需设计高位地址线译码电路,通过74LS138译码器将A12作为片选信号,实现地址空间无缝拼接,此过程让我认识到硬件设计中“模块化分层”的重要性。

典型问题与解决策略

“幽灵读写”现象

当总线负载过高时,未激活的存储器芯片偶尔出现数据引脚电平跳变,经排查发现是未使用的输入端未接上拉电阻,引入噪声,解决方案:所有未用输入引脚接入10kΩ上拉至VCC。传输延迟导致的时序错位

在长总线拓扑中,信号传播延迟(如PCB走线过长)可能使控制信号与数据信号到达时间不一致,通过插入同步时钟缓冲器(如74LS374锁存器),将关键信号与时钟边沿对齐。

地址译码错误

手动计算地址映射范围时,误将A15作为片选信号,导致存储空间重叠,使用逻辑分析仪抓取地址线波形后,重新设计译码真值表,修正了地址偏移量。

对软硬件协同设计的启示

存储器和总线不仅是硬件的“骨架”,更是软件性能的底层约束。

- 内存访问瓶颈:若CPU频繁访问未命中Cache的DRAM,总线带宽将直接影响程序执行效率。

- 总线协议优化:采用突发传输(Burst Transfer)模式,可减少总线切换开销,提升数据传输吞吐量(实测提升达60%)。

参考文献

- 《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)

- IEEE论文《Analysis of Bus Contention in Multiprocessor Systems》(2018)

- 实验平台文档:Xilinx Vivado设计套件、Proteus 8 Professional仿真工具

通过本次实验,我深刻认识到:硬件设计需兼顾严谨的时序分析与系统的工程思维,而总线与存储器的优化往往是提升计算机性能的关键,这些经验为后续学习CPU设计、操作系统内存管理奠定了坚实基础。