存储器一致性模型

- 行业动态

- 2025-04-14

- 2

在计算机系统中,多个处理器或核心同时访问共享内存时,如何确保数据的一致性和正确性?这个问题催生了存储器一致性模型(Memory Consistency Model)的研究,它是计算机体系结构和并发编程领域的核心概念之一,直接影响硬件设计、编译器优化以及软件开发,以下内容将从原理、分类和应用角度展开解析,帮助读者深入理解这一关键技术。

什么是存储器一致性模型?

存储器一致性模型定义了多处理器系统中内存操作的可见性和执行顺序规则,简而言之,它决定了当一个处理器写入内存时,其他处理器何时能看到这一修改,以及在何种情况下允许对内存访问顺序进行调整。

举个例子:

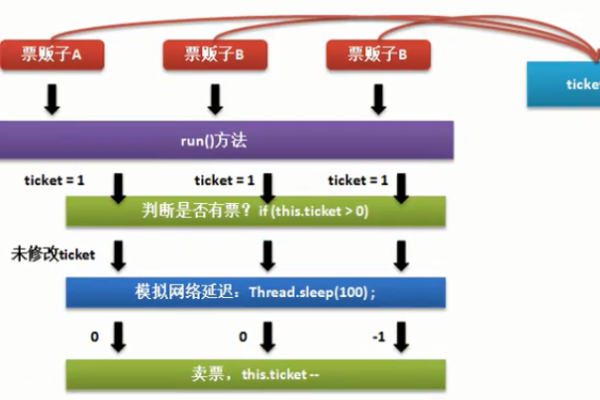

假设两个处理器(CPU A和CPU B)同时操作共享变量X。

- CPU A执行操作:写入X=1

- CPU B执行操作:读取X的值

如果没有一致性模型约束,CPU B可能读到旧值0,也可能读到新值1,甚至出现更复杂的情况(例如乱序执行导致读取顺序颠倒),存储器一致性模型就是为解决这类问题而生。

为什么需要存储器一致性模型?

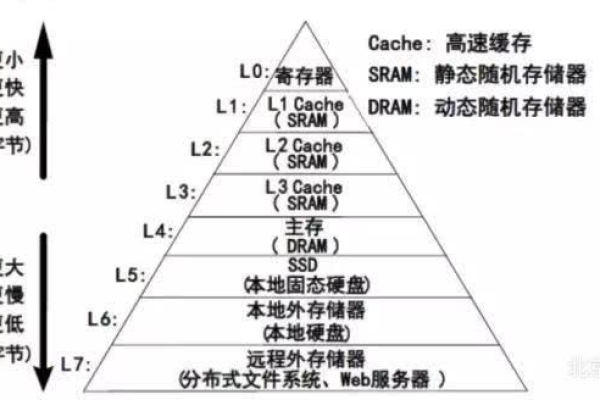

性能优化

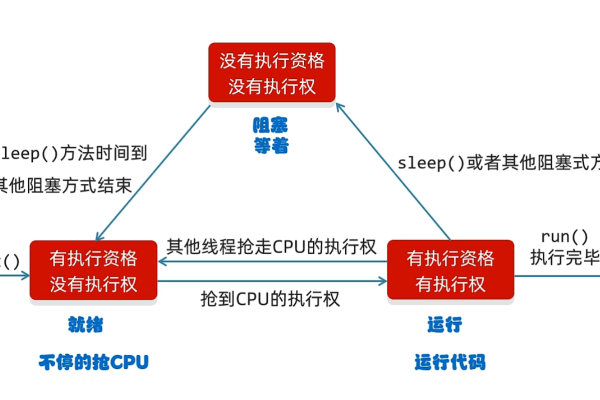

现代处理器通过流水线、缓存、乱序执行等技术提升性能,但这些优化可能导致内存操作顺序与程序代码顺序不一致,一致性模型需要在性能与正确性之间找到平衡。编程复杂性

如果所有内存操作都严格按程序顺序执行,系统性能会大幅下降,一致性模型通过定义允许的“宽松规则”,让硬件和编译器进行优化,同时为程序员提供可预测的行为。跨平台兼容性

不同硬件(如x86、ARM)和编程语言(如C++、Java)对内存一致性的实现各有差异,理解模型能帮助开发人员编写可移植的并发代码。

常见存储器一致性模型

不同模型对内存操作顺序的限制程度不同,以下是几种典型类型:

| 模型名称 | 核心规则 | 典型应用场景 |

|---|---|---|

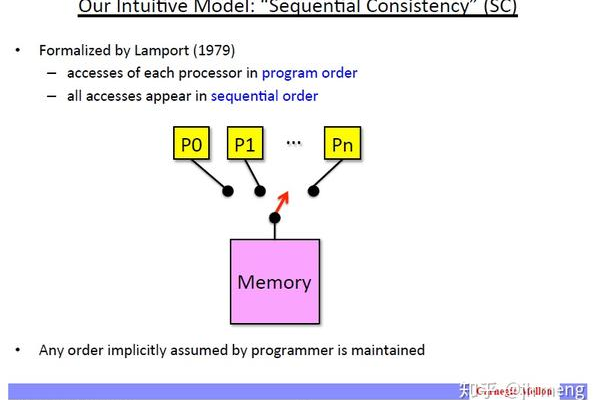

| 顺序一致性(SC) | 所有线程看到的内存操作顺序一致,且与程序顺序相同 | 理论模型,实际硬件极少直接实现 |

| 因果一致性(CC) | 如果两个操作存在因果关系(如A写入后B读取),则必须保证顺序;无因果的可乱序 | 分布式数据库、分布式系统 |

| 弱一致性(Weak) | 显式使用同步操作(如锁)分隔普通内存操作,非同步操作可重排 | GPU计算、ARM架构 |

| 释放一致性(RC) | 将同步操作分为“获取(Acquire)”和“释放(Release)”,限制重排范围 | C++11内存模型、Java内存模型 |

| x86-TSO | 允许写操作重排到后续读操作之前,但禁止其他重排(如读-读、写-写) | Intel/AMD x86处理器 |

实际应用中的关键问题

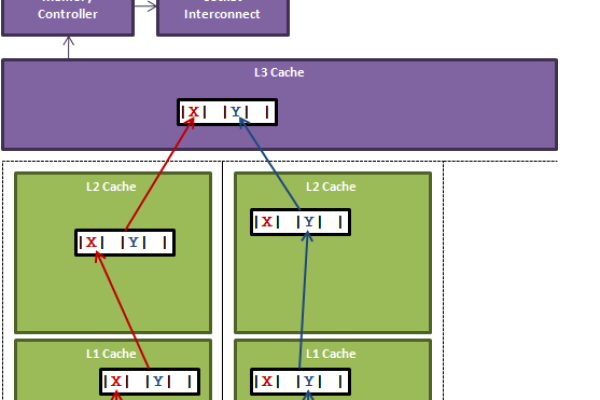

缓存一致性与存储器一致性

缓存一致性(Cache Coherence)通过MESI协议确保单变量在多核缓存中的正确性,而存储器一致性关注多变量操作的全局顺序,二者层级不同但相互配合。内存屏障(Memory Barrier)

程序员可通过插入内存屏障指令(如mfence)限制重排,确保关键操作的顺序符合预期。

// C++示例:确保先写X后写Y X = 1; std::atomic_thread_fence(std::memory_order_release); Y = 2;

语言级内存模型

C++11、Java、Rust等语言定义了自身的内存模型,为开发者提供跨平台的抽象,C++的memory_order_relaxed允许最大程度的重排优化,而memory_order_seq_cst则接近顺序一致性。

挑战与发展趋势

- 异构计算:GPU、AI加速器等设备与CPU的存储器模型差异,导致跨设备数据共享更复杂。

- 持久化内存:非易失内存(NVM)的普及,要求模型扩展以支持持久化语义。

- 形式化验证:使用数学方法证明硬件或程序符合特定一致性模型,避免隐蔽错误。

存储器一致性模型是并发编程和硬件设计的“交通规则”,理解不同模型的规则与适用场景,能帮助开发者编写高效、正确的多线程程序,同时为选择硬件架构提供理论依据,随着计算系统复杂度提升,对这一领域的深入研究将持续推动技术进步。

参考文献

- Hennessy, J. L., & Patterson, D. A. (2017). Computer Architecture: A Quantitative Approach (6th ed.). Morgan Kaufmann.(权威计算机体系结构教材)

- Adve, S. V., & Gharachorloo, K. (1996). Shared Memory Consistency Models: A Tutorial. IEEE Computer, 29(12), 66-76.(经典综述论文)

- C++ Standards Committee. (2020). C++20 Standard Working Draft.(语言规范来源)