如何高效优化存储器访问速度?

- 行业动态

- 2025-04-16

- 2

存储器访问是CPU从内存读写数据的过程,涉及地址总线和数据总线,访问时间、带宽、延迟是关键指标,不同存储类型(如RAM、ROM)的访问方式与性能差异显著,缓存机制通过局部性原理减少访问延迟,优化系统效率,存储器层次结构通过分层管理平衡速度、容量与成本。

从原理到优化的全面解析

在现代计算机系统中,存储器(Memory)是数据存储与处理的核心组件,它的访问效率直接影响系统性能,无论是个人电脑、智能手机,还是云端服务器,存储器的访问机制都是技术设计中的关键环节,本文将深入解析存储器访问的原理、类型及优化方法,帮助读者全面理解这一技术的基础与前沿。

存储器访问的基本原理

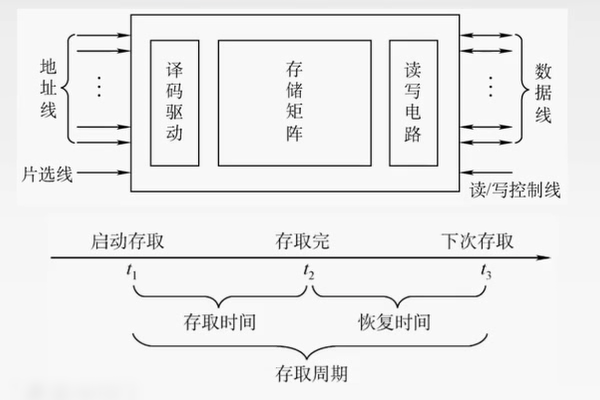

存储器的访问是指处理器(CPU)从存储器中读取数据或向存储器写入数据的过程,这一过程遵循以下步骤:

- 地址译码:CPU通过地址总线发送目标数据的物理地址,存储器控制器解析地址并定位到对应的存储单元。

- 数据传输:数据总线负责将数据从存储器传输到CPU(读操作),或从CPU传输到存储器(写操作)。

- 时序控制:存储器访问需要严格的时钟信号同步,以确保数据的准确性和完整性。

关键参数:

- 访问时间:从发出请求到数据就绪的时间(如DRAM约10-50纳秒,SSD约50-100微秒)。

- 带宽:单位时间内传输的数据量(如DDR4内存带宽可达25.6 GB/s)。

- 延迟:请求发出到开始传输的等待时间,与存储器类型密切相关。

存储器的类型与访问方式

根据存储介质和工作原理,存储器可分为以下几类:

随机存取存储器(RAM)

- 动态RAM(DRAM):需要周期性刷新,成本低、容量大,用于主内存(如电脑内存条)。

- 静态RAM(SRAM):无需刷新,速度快但成本高,多用于CPU缓存。

- 访问特点:支持随机访问,读写速度接近,但断电后数据丢失。

只读存储器(ROM)

- 存储固定程序(如BIOS),数据不可修改或仅能有限写入(如EEPROM)。

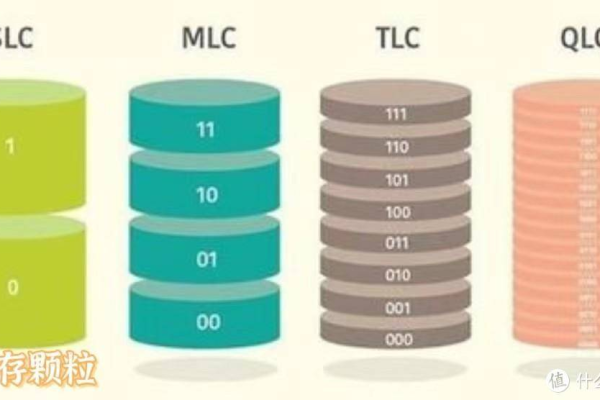

闪存(Flash Memory)

- 非易失性存储,适用于SSD和移动设备。

- 按块擦除,写入速度低于读取速度。

机械硬盘(HDD)

- 通过磁头在旋转磁盘上寻道,顺序访问速度快,随机访问延迟高(毫秒级)。

存储器访问的优化技术

为提高访问效率,计算机系统采用多种优化策略:

缓存技术

- 多级缓存(L1/L2/L3):利用局部性原理(时间局部性、空间局部性),将高频数据保存在靠近CPU的快速缓存中。

- 缓存一致性协议:如MESI协议,确保多核CPU中缓存数据的同步。

预取(Prefetching)

- 预测CPU未来需要的数据,提前加载到缓存中,顺序访问模式下预取相邻地址数据。

内存交织(Memory Interleaving)

- 将内存分为多个存储体,并行访问以提升带宽。

虚拟内存与分页

- 通过页表将物理内存与磁盘空间结合,扩展可用内存容量,但需注意页错误(Page Fault)带来的性能损失。

数据对齐(Data Alignment)

- 将数据存储在地址的整数倍位置,减少CPU访问次数(如32位系统推荐4字节对齐)。

存储器访问的常见问题与解决方案

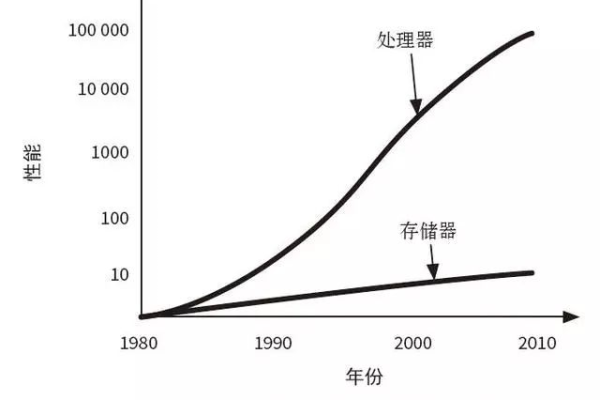

速度瓶颈

- 现象:CPU等待数据时间过长(“内存墙”问题)。

- 方案:升级高带宽内存(如DDR5)、增加缓存容量、使用非均匀内存架构(NUMA)。

数据一致性

- 现象:多核环境下缓存数据不同步。

- 方案:硬件级缓存一致性协议(如Intel QPI总线)、软件级内存屏障指令。

存储器寿命

- 现象:闪存因频繁写入导致寿命缩短。

- 方案:磨损均衡算法(Wear Leveling)、预留OP空间(Over-Provisioning)。

兼容性问题

- 现象:新内存条与旧主板不兼容。

- 方案:检查主板支持的存储器类型(如DDR4/DDR5)、电压和频率匹配。

未来趋势与挑战

- 新型存储技术:如3D XPoint(傲腾)、MRAM(磁阻RAM)等,目标是在速度、容量和非易失性之间取得平衡。

- 存算一体(In-Memory Computing):直接在存储器内部完成计算,减少数据搬运开销,适用于AI和大数据场景。

- 量子存储器:利用量子态存储信息,目前处于实验室阶段,可能彻底改变未来计算架构。

引用说明

本文参考了以下权威资料:

- 计算机体系结构经典教材《Computer Organization and Design》(David A. Patterson, John L. Hennessy)。

- IEEE论文《Memory Technologies for AI Acceleration: A Survey》(2022)。

- 三星、美光等存储芯片厂商的技术白皮书。