存储器内部是如何实现高效工作的?

- 行业动态

- 2025-04-16

- 2

存储器作为现代计算系统的核心部件,其内部实现直接影响着数据存取速度和系统性能,本文将深入解析常见存储器的内部结构和工作原理,帮助读者理解数据如何在硬件层面被存储和调用。

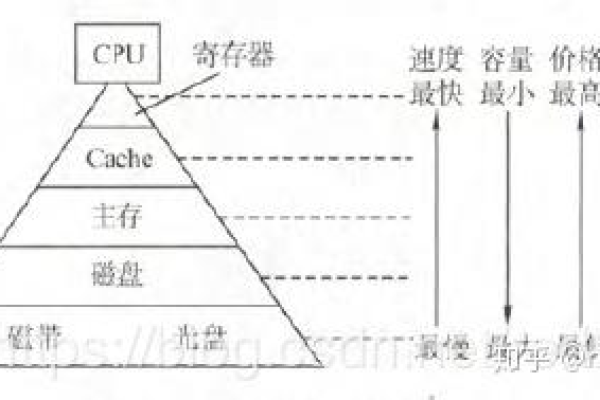

存储器分类与基础结构

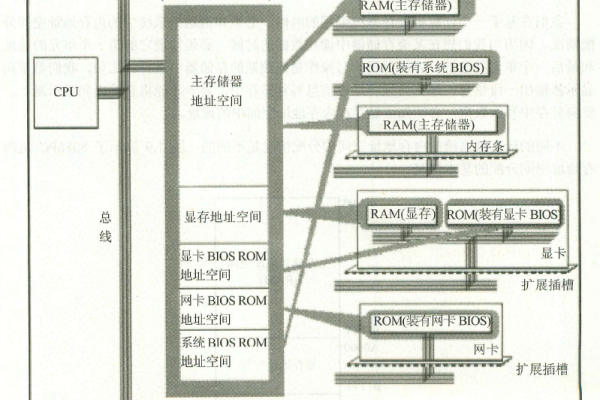

存储器按功能可分为主存储器(如DRAM)和辅助存储器(如SSD、HDD),尽管类型不同,它们的基本实现逻辑均围绕以下核心组件展开:

存储单元(Memory Cell)

- DRAM:通过电容存储电荷(1为高电平,0为低电平),每个单元由一个晶体管和一个电容组成,电容泄漏特性要求定期刷新(Refresh)。

- NAND闪存:采用浮栅晶体管(Floating Gate Transistor),通过捕获电子实现数据持久化,无需刷新。

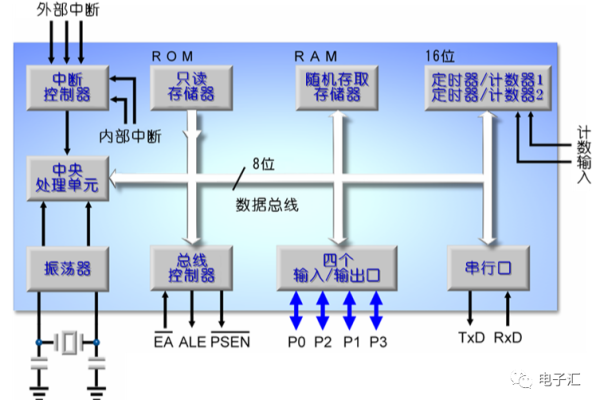

地址解码器(Address Decoder)

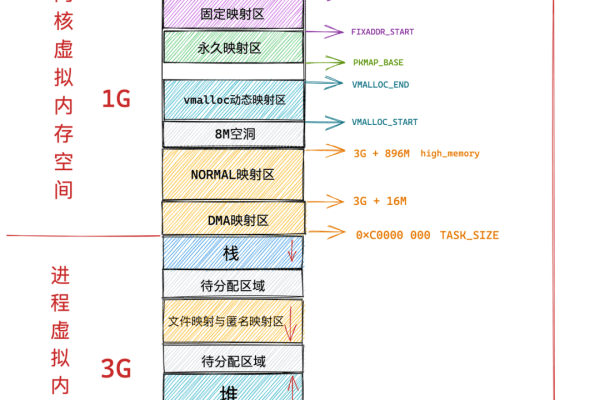

将CPU发送的二进制地址转换为物理存储单元的位置信号,10位地址可解码为2^10=1024个存储单元。读写控制电路

协调数据流向:写入时放大信号强度,读取时检测电荷状态并转换为逻辑值。数据缓冲寄存器

临时存储待写入或读取的数据,减少CPU等待时间。

数据存储的物理实现

DRAM的电荷存储机制

DRAM单元通过电容保存电荷,写入时,字线(Word Line)激活晶体管,位线(Bit Line)向电容充电或放电;读取时,电荷通过位线传输至灵敏放大器(Sense Amplifier),检测电压变化并重构数据。

问题与优化

电容泄漏导致数据丢失,需每隔64ms刷新一次,现代DRAM采用Bank分组刷新技术,减少性能损失。

NAND闪存的浮栅晶体管

浮栅晶体管通过绝缘层(如二氧化硅)捕获电子:

- 写入(Program):高压使电子穿过绝缘层,滞留在浮栅中,改变晶体管的阈值电压。

- 擦除(Erase):施加反向电压,释放浮栅中的电子。

多层单元技术(QLC)

通过区分4种电荷状态(00/01/10/11),单单元可存储4比特数据,但读写复杂度显著上升。

存储器的读写过程

读取操作

- CPU发送地址至存储器控制器。

- 地址解码器定位目标存储单元。

- 灵敏放大器检测电荷状态,输出数字信号。

- 数据通过总线返回CPU。

写入操作

- 数据缓冲寄存器接收待写入内容。

- 地址解码器选择目标单元。

- 写入电路施加电压,修改存储单元状态(如电容充电)。

SSD的写放大问题

由于NAND闪存需按块擦除,小数据写入可能导致整块重写,主控芯片通过FTL(Flash Translation Layer)优化写入路径,降低损耗。

技术演进:从平面到3D堆叠

2D NAND的局限性

制程微缩至15nm后,单元间干扰(Cell-to-Cell Interference)加剧,可靠性下降。

3D NAND突破

将存储单元垂直堆叠,如三星V-NAND技术可堆叠200层以上,容量提升同时降低单位成本。新兴存储器技术

- MRAM(磁阻存储器):通过磁化方向存储数据,兼具非易失性与高速特性。

- PCM(相变存储器):利用硫族化合物晶态/非晶态电阻差异,读写速度接近DRAM。

应用场景与选型建议

- 高频计算(如AI训练):优先选择DRAM或HBM(高带宽存储器)。

- 数据中心存储:3D TLC/QLC SSD平衡成本与性能。

- 物联网设备:NOR闪存支持XIP(就地执行),降低功耗。

存储器的内部实现融合了半导体物理、电路设计与材料科学的创新,从电容充放电到电子捕获,从平面工艺到3D堆叠,技术进步不断突破容量与速度的边界,理解这些原理,有助于在开发中优化数据存取策略,提升系统整体效率。

参考文献

- IEEE Spectrum. (2025). 3D NAND Technology: Challenges and Innovations.

- Micron Technology. (2022). DRAM Architecture White Paper.

- Samsung Electronics. (2021). V-NAND Technical Brief.