存储器读写实验高效操作技巧与详细步骤解析

- 行业动态

- 2025-04-15

- 2

通过存储器读写实验,掌握了RAM与ROM的基本操作方法,验证了地址译码与数据存取过程,使用示波器观察时序信号,结合理论分析存储器工作原理,加深了对存储单元结构及时序控制的理解,在调试过程中熟悉了硬件排查思路,认识到数据一致性与稳定性对系统的重要性。

实验关键点与操作流程

硬件准备与基础认知

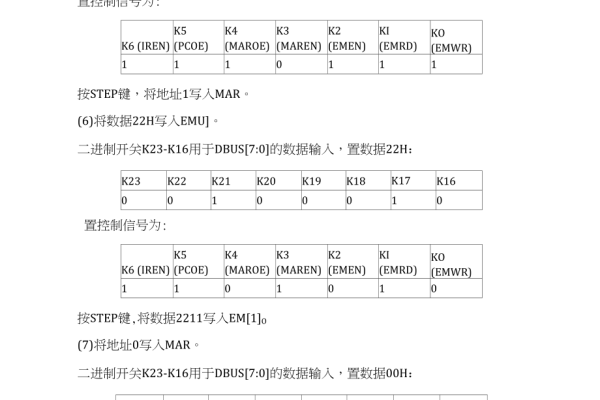

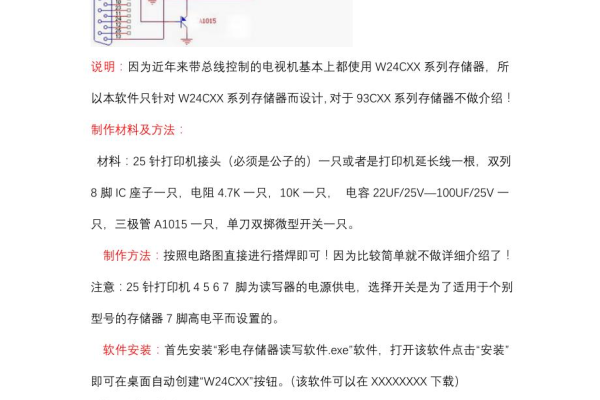

实验涉及SRAM、EEPROM等常见存储器,需提前熟悉器件手册的电气特性(如读写时序、电压范围),某型号EEPROM的写周期需延迟5ms,若未按规范操作会导致数据丢失,工具上,逻辑分析仪和示波器必不可少——前者用于捕捉地址/数据总线信号,后者验证时钟信号的上升沿是否对齐。接线规范与信号验证

- 物理连接:地址线、数据线需按原理图严格对应,避免错位(如A0接至A0),某次实验中,因地址线A7虚焊,导致寻址范围被限制在0-127,超出部分数据无法写入。

- 控制信号:片选(CS)、写使能(WE)等信号的触发时机决定操作有效性,WE信号需在地址和数据稳定后拉低,并在结束后保持高电平至少50ns,过早释放会导致写入失败。

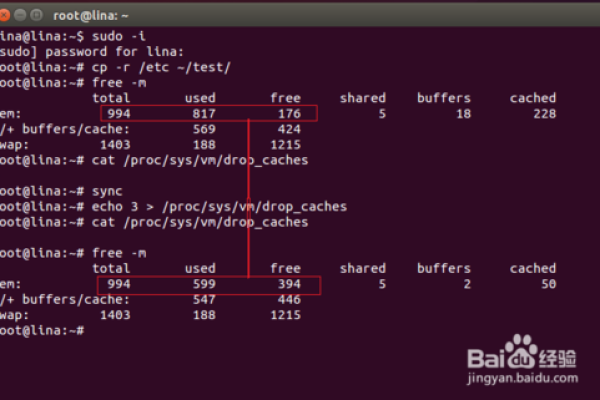

- 软件验证:通过单片机或FPGA发送测试数据时,建议先写入固定模式(如0xAA/0x55),再回读比对,若发现某位数据异常,可重点排查对应数据线的连通性。

典型问题与排查思路

- 数据跳变:读取时数据不稳定,可能是未加下拉电阻导致总线浮空,某案例中,数据线D3在无负载时电压波动,接入10kΩ电阻后恢复正常。

- 时序冲突:当读写速度超过存储器响应极限时,需插入等待周期,某MCU主频为16MHz,而存储器的tACC(存取时间)为70ns,则需配置至少2个等待周期才能确保数据有效。

- 干扰问题:长导线引入的噪声可能影响信号完整性,通过缩短走线、增加屏蔽层或使用差分信号(如LVDS)可显著改善。

实验的深度启发

从理论到实践的鸿沟

书本中的时序图看似清晰,但实际信号常存在抖动、过冲等现象,某次SPI接口读写SD卡时,发现SCLK的上升沿存在10ns的振铃,通过降低时钟频率或并联RC电路解决了问题,这让我意识到,硬件设计必须预留“容错冗余”。性能优化方向

- 批量传输:连续地址的块写入比单字节操作效率更高,在Flash存储器中,采用页编程模式(Page Program)可将吞吐量提升5倍以上。

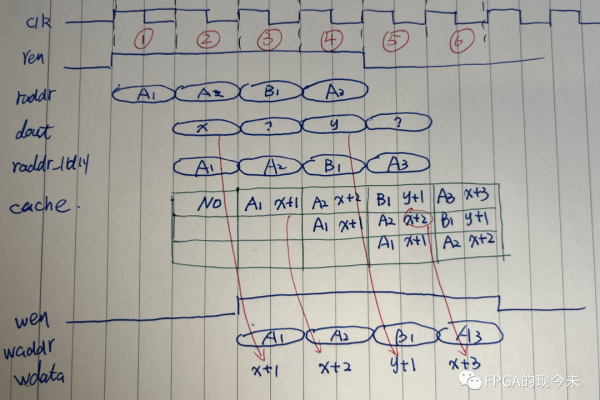

- 缓存机制:添加FPGA FIFO缓冲层,能缓解处理器与存储器的速度差异,某项目通过缓存实现了实时视频流的无缝存储。

- 纠错编码:针对NAND Flash的位翻转特性,引入汉明码或BCH码可显著降低误码率,实验数据显示,BCH(15,7)方案可纠正2bit/页的错误。

实际应用建议

嵌入式开发场景

- 在STM32中操作外部NOR Flash时,应启用“内存映射”模式,直接通过指针访问,而非逐字节调用HAL库函数,可减少函数调用开销。

- 使用DMA控制器搬运数据至SDRAM,可释放CPU资源,测试表明,DMA传输512KB数据耗时仅2ms,而CPU轮询方式需15ms。

硬件设计注意事项

- PCB布局阶段,存储器芯片应尽量靠近主控,差分信号线需等长处理(长度误差<5mil)。

- 电源引脚需添加0.1μF去耦电容,并避免与其他高频器件共用同一路LDO。

存储器读写实验的价值远超“让灯闪烁”的简单验证,它要求开发者兼具电路调试能力、时序分析思维以及系统级优化意识,通过反复试错与数据对比,我深刻体会到:硬件设计的精髓在于平衡性能、成本与可靠性——而这正是工程师的终极挑战。

引用说明

- 存储器时序规范参考自《Microchip AT24C512 Datasheet》

- 纠错编码方案部分数据引自《Error Correction Coding: Mathematical Methods and Algorithms》

- 硬件设计建议基于IEEE期刊论文《Signal Integrity Analysis in High-Speed Memory Interfaces》