存储器芯片串联并联区别与优势详解 如何选择与应用技巧全解析

- 行业动态

- 2025-04-15

- 2

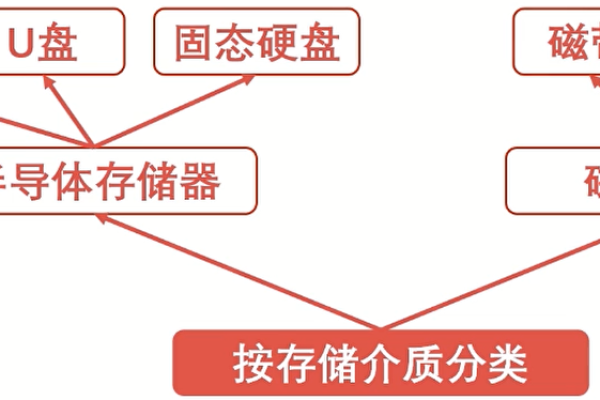

存储器芯片串联通过依次连接扩展总容量,共享总线但访问速度受限;并联则同时连接多个芯片,提升数据吞吐量与并行处理效率,但需复杂控制,串联适用于低成本容量扩展,并联适合高性能计算,两者结合可优化存储系统性能。

在计算机硬件设计与嵌入式系统中,存储器芯片的串联(Cascade)与并联(Parallel)是两种核心的扩展技术,它们直接影响系统的存储容量、数据吞吐量和运行效率,本文将通过技术原理、应用场景与优劣势对比,为读者解析这两种配置方式的关键细节。

存储器芯片的基础结构

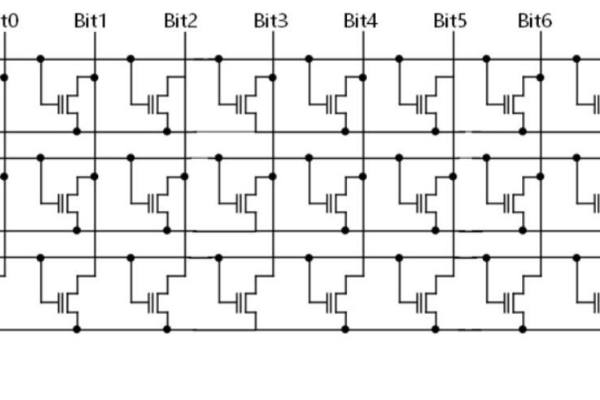

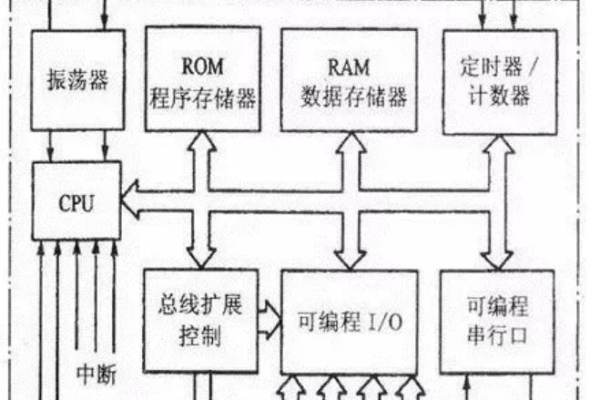

存储器芯片(如DRAM、SRAM、NAND Flash)通过控制信号(地址线、数据线、读写使能)与主控芯片交互。

- 地址线:决定存储单元的访问位置

- 数据线:传输读取或写入的二进制数据

- 控制逻辑:协调时序与操作模式

串联(Cascade)连接的原理与实现

串联指多个存储器芯片通过层级式地址扩展共享同一组数据总线,但分时复用控制信号。

工作流程

- 地址分配:主控芯片通过高位地址线选择目标芯片

2片16MB芯片串联时,地址线A24作为片选信号(0选第一片,1选第二片)

- 分时访问:同一时刻仅一个芯片处于激活状态

- 数据交互:选中的芯片通过共享数据总线传输数据

典型应用

- 单片机系统:扩展外部RAM时受限于地址线数量(如8051的16位地址线最大支持64KB)

- FPGA开发板:通过多级串联实现大容量缓存

优劣势对比

| 优势 | 劣势 |

|---|---|

| 节省数据线资源 | 总带宽受限于单通道 |

| 降低主控芯片引脚压力 | 增加地址译码电路复杂度 |

| 扩展容量灵活 | 多芯片切换引入延迟 |

并联(Parallel)连接的原理与实现

并联指多芯片同时接入数据总线,通过增加数据线位数提升吞吐量。

工作模式

- 位扩展:多芯片并行输出数据位

4片8位芯片并联可组成32位数据总线

- 同步操作:所有芯片接收相同的地址与控制信号

- 带宽倍增:单次操作可读写多倍数据量

典型应用

- DDR内存模组:8颗x8芯片并联实现64位总线

- SSD主控设计:多通道NAND并联提升读写速度(如PCIe 4.0 x4接口)

优劣势对比

| 优势 | 劣势 |

|---|---|

| 带宽线性增长 | 数据线需求翻倍 |

| 降低单芯片负载压力 | 功耗与发热量增加 |

| 冗余设计提升可靠性 | 主控需支持多通道管理 |

关键参数对比表

| 维度 | 串联 | 并联 |

|---|---|---|

| 容量扩展 | 叠加式(32MB+32MB) | 独立式(单芯片容量) |

| 速度影响 | 增加片选延迟 | 带宽翻倍 |

| 功耗 | 单芯片工作,功耗低 | 多芯片并发,功耗高 |

| 成本 | 需译码器 | 需更多布线资源 |

实际工程中的混合架构

高端存储系统常采用串并联混合设计:

- SSD中的NAND堆叠:

- 横向并联多通道(如8通道)

- 纵向串联多Die(如4层3D NAND)

- 服务器内存板:

- 并联提高带宽(DDR4 3200MHz x4)

- 串联扩展容量(单条128GB)

选型决策建议

- 优先并联的场景:

- 高实时性需求(工业控制、GPU显存)

- 主控支持多通道(如ARM Cortex-A系列)

- 优先串联的场景:

- 引脚资源受限(低端MCU)

- 成本敏感型产品(消费电子)

引用说明

- 美光科技《DDR4 SDRAM数据手册》

- JEDEC固态技术协会JESD209-5C标准

- 三星电子《3D NAND技术白皮书》

- IEEE《高性能存储系统设计》(Transaction on VLSI, 2021)

结束)