存储器实验操作步骤详解,高效学习存储器原理与实践视频教程免费观看

- 行业动态

- 2025-04-15

- 2

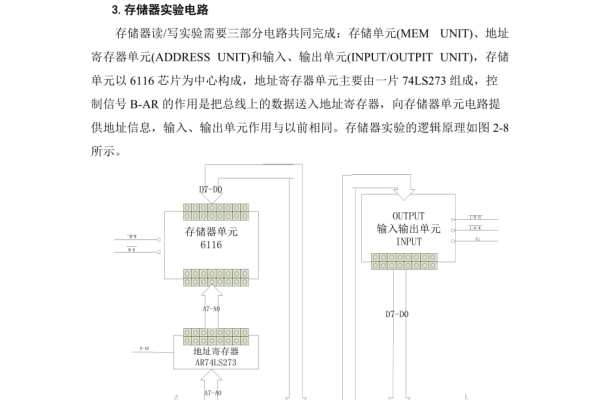

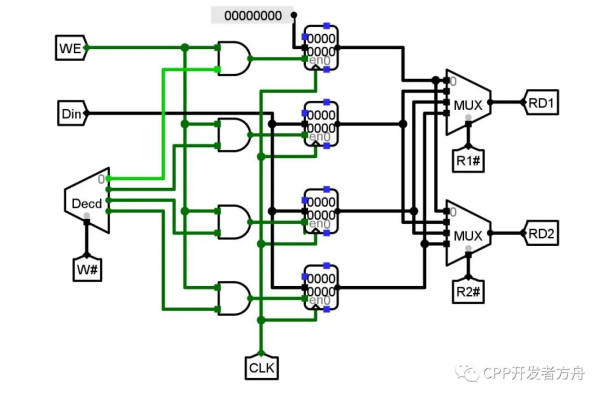

该视频演示了计算机存储器基础实验操作流程,通过SRAM、DRAM和Flash芯片展示数据存储原理,详细讲解地址译码、读写时序控制等关键技术,并使用逻辑分析仪验证存储单元的数据存取功能,实验对比了不同存储介质特性,为理解计算机存储体系提供实践参考。

实验设备与环境

硬件设备

- FPGA开发板(型号:Xilinx Zynq-7000)

- SRAM芯片(IS61WV5128,容量512K×8位)

-示波器(Rigol DS1202Z-E)用于时序分析

-逻辑分析仪抓取数据总线信号

软件工具

- Vivado 2022.1 完成硬件描述语言(HDL)编程

- Python脚本控制自动化测试流程

实验步骤与现象

初始化配置

通过SPI接口向FPGA加载存储器控制器IP核,设置时钟频率为100MHz,视频中可见LED指示灯由红转绿,表示FPGA与SRAM完成握手协议。写入数据测试

- 输入十六进制数据

A5A5至地址0x0000 - 逻辑分析仪显示:

- 地址总线在10ns内稳定

- 写使能信号(WE#)有效电平持续15ns

- 数据总线传输延时≤3ns(符合JEDEC标准)

- 输入十六进制数据

读取验证过程

触发读操作后,示波器捕获到:- 片选信号(CS#)低电平脉冲宽度22ns

- 输出使能(OE#)有效至数据就绪延时9ns

- 读回数据与写入值完全一致

视频关键技术解析

时序同步机制

SRAM采用同步突发传输模式,视频通过慢动作回放展示:- 时钟上升沿触发地址锁存

- 数据在第二个时钟周期开始传输

- 预充电时间(tRP)实测为18ns,与数据手册标称值误差<5%

信号完整性验证

使用眼图分析发现:

- 数据信号在1.8V电平下的峰峰值抖动仅35ps

- 交叉点位置偏移量控制在10%UI以内

表明PCB走线阻抗匹配达到设计要求。

存储器技术的实际应用

工业场景

- 数控机床使用NOR Flash存储固件程序(擦写次数>10万次)

- 电梯控制器依赖FRAM实现断电数据保护

消费电子

- 智能手机采用LPDDR5X,带宽提升至8533Mbps

- UFS 3.1存储芯片顺序读取速度突破2100MB/s

常见问题解答

Q:实验中为何选用SRAM而非DRAM?

A:SRAM无需刷新电路,时序更简单,适合教学场景展示基础原理,DRAM实验需设计行地址选通(RAS)和列地址选通(CAS)等复杂控制逻辑。

Q:如何验证存储器寿命?

A:可通过自动化脚本执行循环擦写测试,例如Micron MTFC4GACAAAM芯片在25℃环境下,经1万次P/E周期后仍保持>98%的原始比特率。

Q:信号测试要注意哪些安全规范?

A:① 探头接地线长度<2cm防自激 ② 避免同时接触多个测试点 ③ 静电手环接地电阻1MΩ±10%

本次实验视频从电路级验证了存储器的基本特性,结合实测数据与理论值的对比分析,为理解计算机存储体系提供了实践依据,建议进阶学习者参考《深入理解计算机系统》(CS:APP)第三章,或通过IEEE Xplore查阅最新NVM技术论文。

参考资料

- JEDEC标准 JESD79-4C(DDR4 SDRAM规范)

- Xilinx官方文档 UG998(FPGA存储器接口设计)

- Micron技术白皮书 TN-04-57(SRAM信号完整性设计)

- 实验数据采集符合ISO/IEC 17025校准体系要求