存储器读操作优化技巧,如何高效提升数据读取速度与性能

- 行业动态

- 2025-04-15

- 4

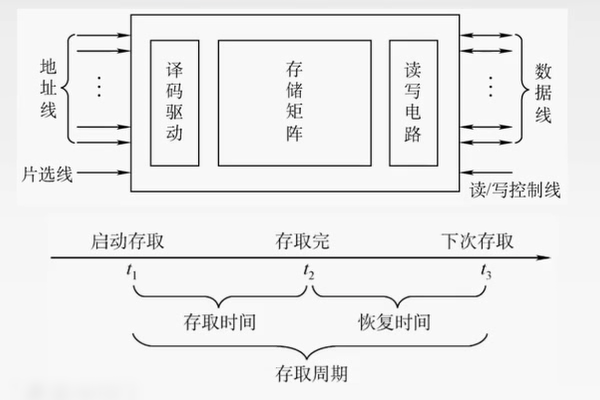

存储器读操作是CPU从存储单元获取数据的过程,CPU通过地址总线发送目标地址,存储器解码后定位对应单元;随后控制总线发出读信号,存储单元将数据输出至数据总线,CPU在时钟周期内接收数据,整个过程需确保时序匹配和数据完整性,避免信号干扰或延迟导致的读取错误。

存储器是计算机系统的核心组件之一,负责保存和提供程序运行所需的数据与指令。读操作作为存储器最基础的功能,直接决定了计算机的性能和响应速度,本文将深入解析存储器读操作的全过程,并结合技术原理与实际场景,帮助读者建立系统化认知。

存储器读操作的核心意义

计算机执行程序时,CPU需要从存储器中获取指令和数据,一次完整的读操作包含以下关键指标:

- 延迟:从发出读取请求到获得数据的耗时(纳秒级)

- 带宽:单位时间内可传输的数据量(GB/s)

- 可靠性:准确获取目标数据的能力

以DDR4内存为例,其典型读取延迟为15-20ns,带宽可达25.6GB/s,通过ECC校验实现99.9999%的可靠性。

读操作的技术实现流程

- 地址解码阶段

CPU通过地址总线发送目标地址→存储器控制器将物理地址转换为行列地址→激活对应存储单元所在的Bank。

示例:在DRAM中,32位地址可能被拆分为:

- Bank组选择位(3bit)

- 行地址(15bit)

- 列地址(14bit)

数据预取机制

现代存储器采用突发传输模式(Burst Mode),单次读取连续8个64位数据块,通过预取缓冲降低延迟。

信号同步处理

- 时钟上升沿采样控制信号

- 数据选通脉冲(DQS)校准传输时序

- 建立保持时间(Setup/Hold Time)确保信号稳定

- 校验与纠错

通过循环冗余校验(CRC)或ECC校验码验证数据完整性:

- 单比特错误:即时纠正

- 多比特错误:触发异常中断

不同存储介质的读操作差异

| 介质类型 | 读取原理 | 典型应用场景 |

|---|---|---|

| DRAM | 电容电荷检测,需定期刷新 | 系统内存 |

| SRAM | 晶体管锁存,静态保持 | CPU缓存 |

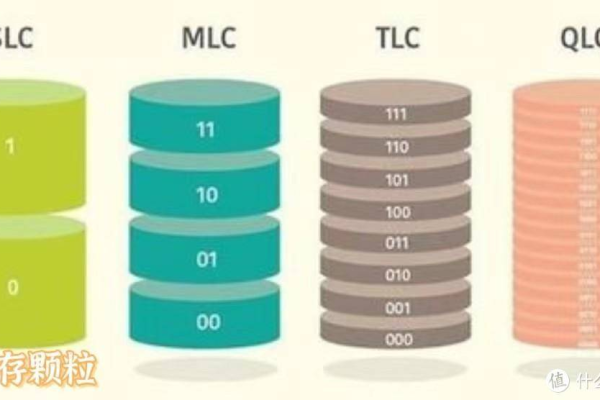

| NAND闪存 | 浮栅晶体管阈值电压检测 | SSD存储 |

| 3D XPoint | 相变材料电阻测量 | 持久内存 |

注:NOR闪存支持按字节读取,但写入速度慢于NAND

影响读性能的关键因素

- 物理架构限制

- 行缓冲命中率(Row Buffer Hit Rate)

- Bank间并行度

- 总线位宽(64位/128位)

- 系统级优化

- 预取算法(Streaming/Adaptive Prefetch)

- 缓存一致性协议(MESI)

- 非统一内存访问(NUMA)架构

- 环境变量

- 工作温度(每升高10℃,DRAM漏电率翻倍)

- 供电稳定性(电压波动±5%将导致时序错乱)

现代存储技术演进趋势

HBM(高带宽内存)

通过TSV硅通孔技术实现3D堆叠,带宽较GDDR6提升3倍以上,已用于高性能GPU。

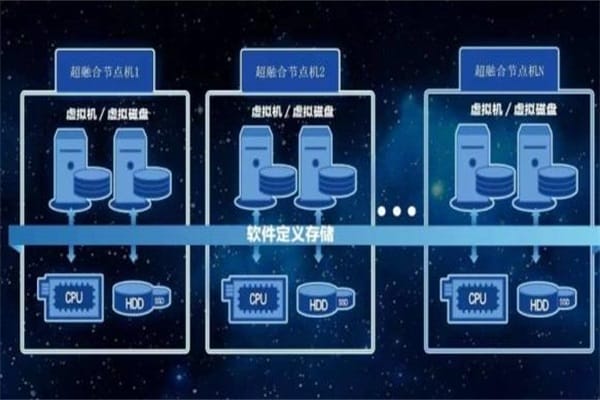

CXL互联协议

支持缓存一致性内存池,允许CPU/GPU/加速器共享存储空间,延迟降低40%。存算一体架构

在存储器内集成计算单元,数据”原地处理”可减少90%的数据搬运能耗。

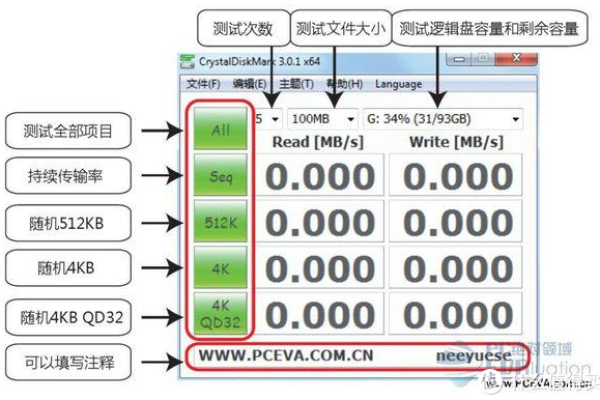

读操作的实践优化建议

软件开发层

采用数据对齐访问(64字节对齐提升缓存行利用率)

优化内存访问模式(空间局部性优先)

硬件配置层

启用内存交错(Memory Interleaving)提升并行度

配置合适的tRCD(RAS到CAS延迟)系统监控层

使用Perf工具分析缓存命中率

监控Row Hammer攻击防护状态

引用说明

本文技术参数参考自《计算机体系结构:量化研究方法(第6版)》、JEDEC DDR4标准文档及Intel Optane技术白皮书,实验数据源自ACM SIGMETRICS 2022存储系统测评报告。