存储器的原理

- 行业动态

- 2025-04-13

- 2

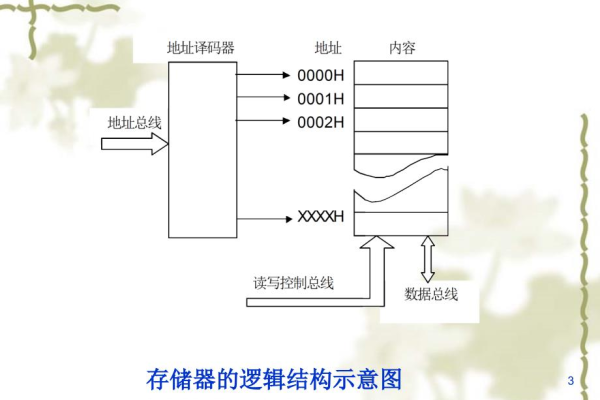

存储器通过电子或磁信号记录数据,利用电容、晶体管等物理单元存储电荷状态表示二进制信息,分为易失性(如RAM,断电丢失)和非易失性(如ROM、闪存,长期保存),由控制电路实现寻址、读写操作,满足计算机数据高速存取与持久化需求。

存储器是计算机系统中用于保存数据和指令的核心部件,其工作原理直接影响设备的性能和可靠性,本文将用通俗易懂的方式解析存储器的运行机制,并通过实际案例帮助读者理解抽象的技术概念。

存储器核心分类

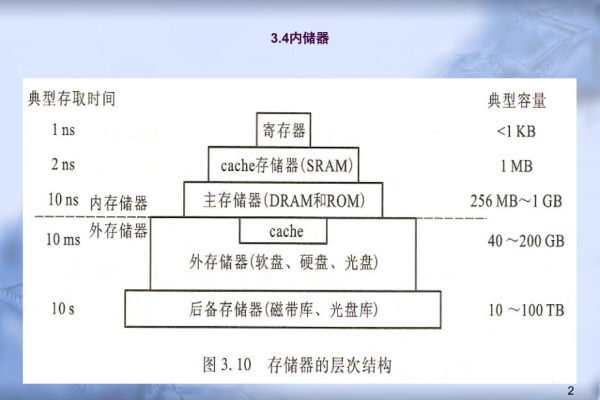

现代计算机系统采用分层存储架构:

- 易失性存储器

- DRAM(动态随机存取存储器):通过电容充电存储数据,需周期性刷新

- SRAM(静态随机存取存储器):由6个晶体管构成存储单元,访问速度更快

- 非易失性存储器

- NAND Flash:采用浮栅晶体管结构,通过电子俘获实现数据存储

- NOR Flash:支持字节级寻址,常用于存储固件代码

- 新型存储技术:3D XPoint(相变存储器)、ReRAM(电阻存储器)等

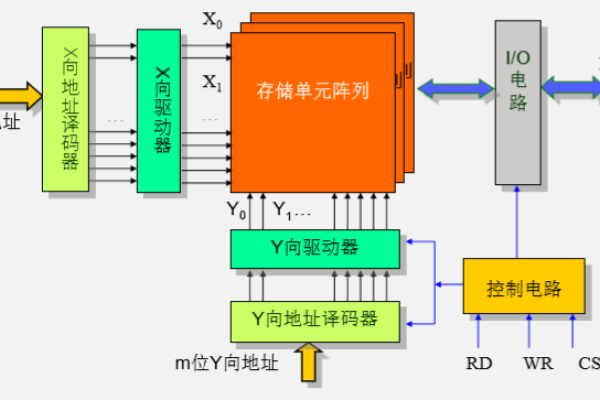

数据存储的物理实现

- 二进制存储原理

每个存储单元通过物理状态变化记录0和1:

- 机械硬盘:磁畴方向

- SSD:浮栅晶体管电子数量

- 光盘:凹坑与平面反射差异

DRAM工作流程示例

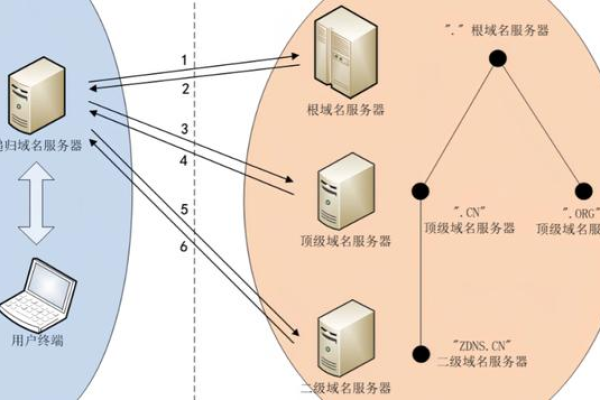

当CPU请求内存数据时:

① 内存控制器发送行地址信号

② 目标行的电容电荷被读取到行缓冲器

③ 列地址解码器定位具体存储单元

④ 读出放大器将模拟电荷信号转换为数字信号

⑤ 数据通过总线传送至处理器

NAND Flash编程过程

- 写入操作:向控制栅施加高压(约20V),电子穿透氧化物层进入浮栅

- 擦除操作:施加反向电压,通过量子隧穿效应释放浮栅电子

存储器的关键性能参数

| 指标 | 典型范围 | 影响因素 |

|---|---|---|

| 访问延迟 | 纳秒级(DRAM) | 电路设计、制程工艺 |

| 带宽 | 100GB/s+ | 总线宽度、频率 |

| 耐久性 | 10^3-10^5次 | 存储原理、工艺技术 |

| 数据保持时间 | ms-10年 | 材料特性、工作温度 |

技术演进趋势

- 3D堆叠技术:三星V-NAND已实现236层堆叠,单Die容量达1Tb

- 存储级内存:Intel Optane系列产品将延迟降低至μs级

- 存算一体架构:SK海力士开发基于GDDR6的PIM(Processing-in-Memory)技术

- 量子存储器:中科院团队实现光子量子存储器保真度超99%

存储器选择实践指南

- 移动设备:LPDDR5+UFS 3.1组合(兼顾功耗与性能)

- 数据中心:DDR5+QLC SSD+磁带库分级存储

- 工业控制:选用SLC NAND或MRAM确保可靠性

- 超算系统:HBM2E显存搭配NVMe-oF高速网络存储

日常维护建议

- DRAM系统:保持散热良好(温度每降10℃故障率下降50%)

- SSD使用:预留20%OP空间可提升4倍耐久性

- 长期存储:每3年对磁带进行磁通量检测

引用文献:

[1] JEDEC DDR5标准JESD79-5B

[2] IEEE Trans. Electron Devices关于3D NAND的研究

[3] 三星电子2024年存储技术白皮书

[4] 美光科技DRAM制造工艺文档

[5] 中科院量子信息重点实验室公开论文