存储器地址怎么搭建

- 行业动态

- 2025-04-14

- 2

存储器地址通过地址总线和地址解码器实现搭建,地址总线传递二进制地址信号,解码器将地址转换为对应存储单元的选通信号,确保每个存储单元拥有唯一访问路径,地址位数决定可寻址空间大小,需根据存储容量合理设计总线宽度与解码逻辑。

存储器地址搭建的核心原理与实践流程

存储器地址是计算机系统中用于定位数据存储位置的核心机制,其搭建涉及硬件设计、地址分配逻辑及软件协同工作,以下是搭建过程的详细解析,适用于嵌入式系统、计算机组成原理等场景。

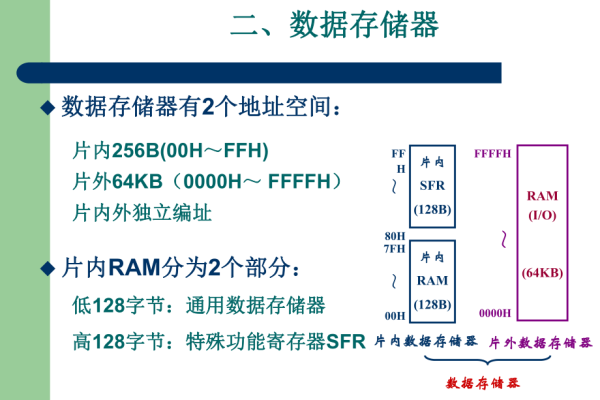

存储器地址的基础概念

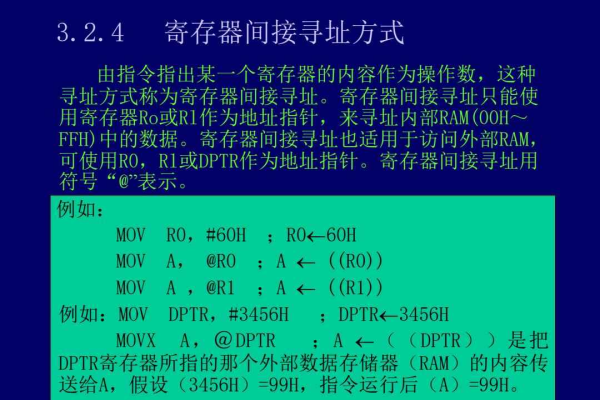

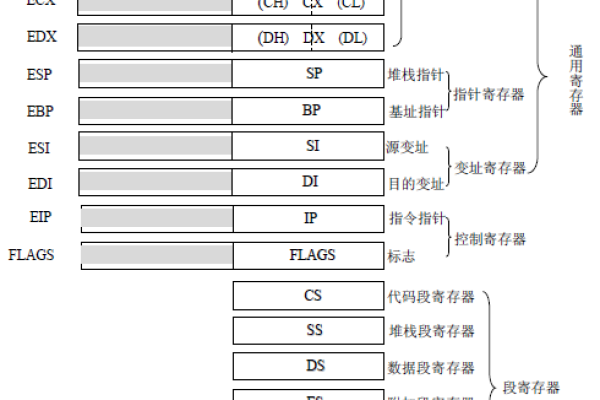

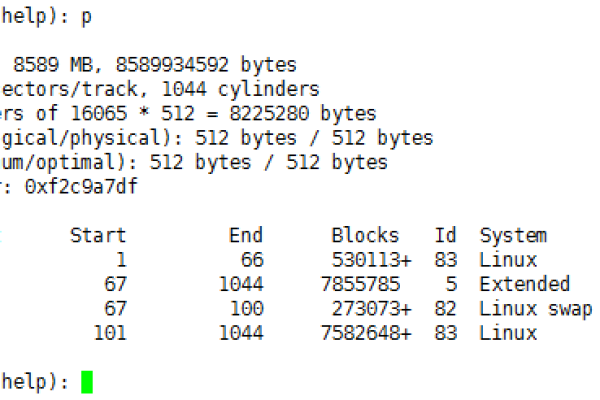

存储器地址由二进制数值表示,对应存储单元的物理或逻辑位置,地址空间的大小由地址总线的位数决定,

- 16位地址总线 → 寻址范围为0x0000至0xFFFF(64KB)

- 32位地址总线 → 寻址4GB空间

关键术语:

- 物理地址:硬件实际使用的存储位置。

- 逻辑地址:软件层面通过分段或分页机制生成的地址。

- 地址解码器:将CPU发出的地址信号转换为具体存储单元的控制信号。

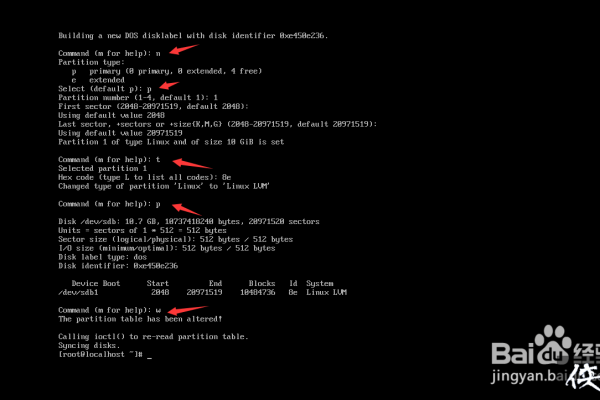

搭建存储器地址的步骤

确定硬件需求

- 地址总线宽度:根据系统需求选择(如8/16/32位)。

- 存储器类型:如RAM、ROM、Flash,需匹配访问速度和容量。

- 地址解码电路:使用逻辑门(如与门、或门)或可编程芯片(如CPLD)实现。

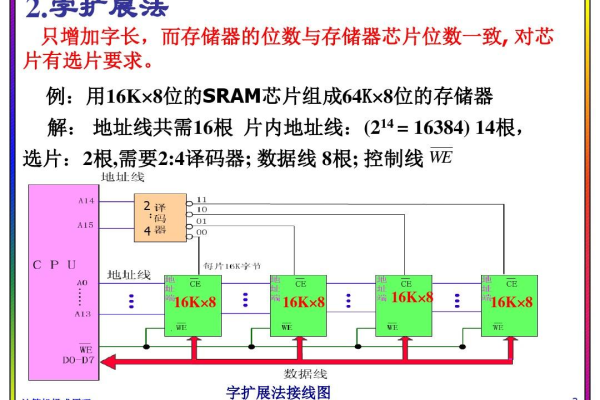

设计地址分配方案

- 线性分配:直接按顺序为每个存储单元分配连续地址(适合单一存储器)。

- 块分配:将地址空间划分为多个块,

- 0x0000-0x7FFF:主存储器

- 0x8000-0xFFFF:外设寄存器

构建地址解码逻辑

- 门电路解码:通过组合逻辑生成片选信号(如用74LS138芯片实现3-8译码器)。

- 可编程逻辑:通过FPGA或CPLD实现灵活地址映射,支持动态调整。

示例电路:

地址总线 → 译码器 → 片选信号(CS)

数据总线 ↔ 存储器

控制总线(读/写信号) → 存储器的OE(输出使能)、WE(写入使能) 验证与调试

- 逻辑分析仪:抓取地址总线和控制信号,确认时序符合存储器规格。

- 测试代码:通过写入/读取特定地址的数据,验证地址分配是否正确。

测试代码示例(C语言):

volatile uint8_t *mem_addr = (uint8_t*)0x8000;

*mem_addr = 0xAA; // 写入数据

if (*mem_addr == 0xAA) { /* 验证成功 */ } 常见问题与解决方案

地址冲突

- 现象:多个设备响应同一地址。

- 方案:检查译码逻辑,确保片选信号互斥;使用更复杂的译码器(如4-16译码器)。

时序不匹配

- 现象:存储器读写失败。

- 方案:调整CPU时钟或添加等待状态(Wait State),延长访问周期。

地址空间浪费

- 现象:未充分利用可用地址范围。

- 方案:采用部分地址译码或动态重映射技术(如Bank Switching)。

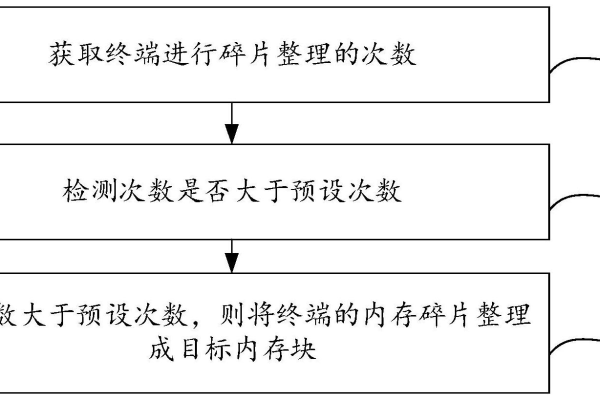

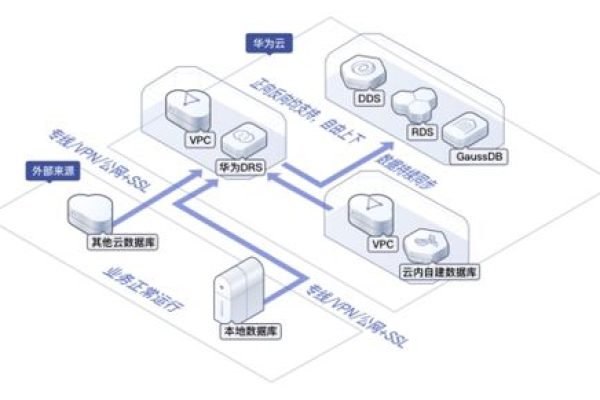

现代系统中的地址管理

- 虚拟内存机制:通过MMU(内存管理单元)将逻辑地址转换为物理地址,支持分页和权限控制。

- 内存映射外设:将外设寄存器映射到地址空间,统一访问方式(如ARM Cortex-M系列)。

存储器地址搭建是硬件与软件协同设计的过程,需严谨规划地址分配、解码逻辑及验证流程,对嵌入式开发者而言,理解地址空间的划分和译码原理是优化系统性能的关键。

引用说明

- [1] 《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)

- [2] IEEE标准《微处理器系统总线规范》(IEEE 1394)

- [3] 存储器芯片数据手册(如Micron MT48LC32M8A2)