存储器地址 重叠

- 行业动态

- 2025-04-12

- 2

什么是存储器地址重叠?

存储器地址重叠(Memory Address Overlapping)指的是在计算机系统中,不同的逻辑地址(或虚拟地址)映射到同一物理存储单元的现象,多个“门牌号”(逻辑地址)指向了同一个“房间”(物理存储空间),这种情况可能由硬件设计、系统架构或编程错误导致。

为什么会出现地址重叠?

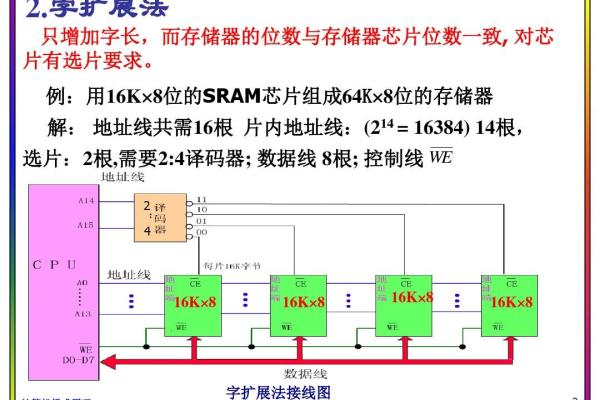

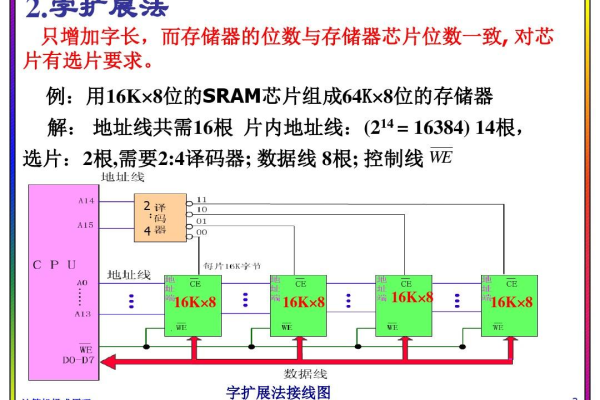

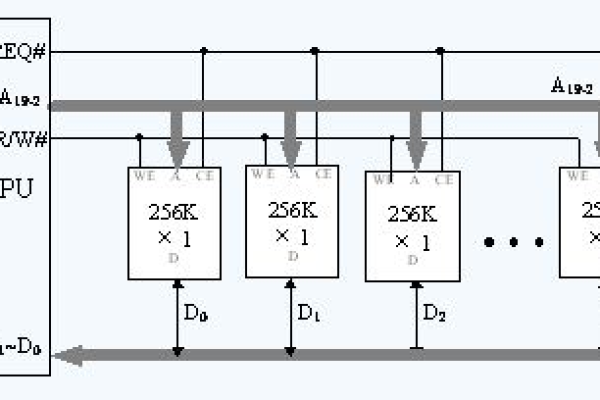

总线宽度与地址解码限制

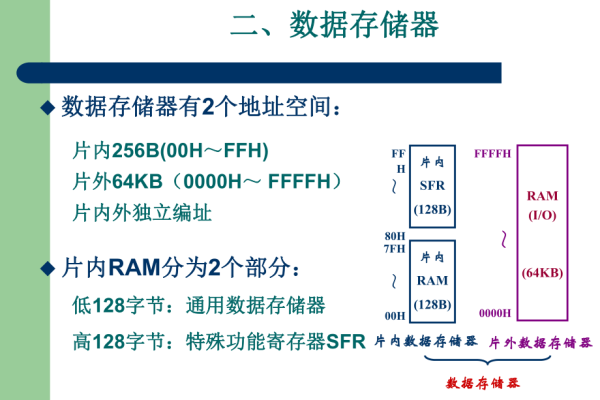

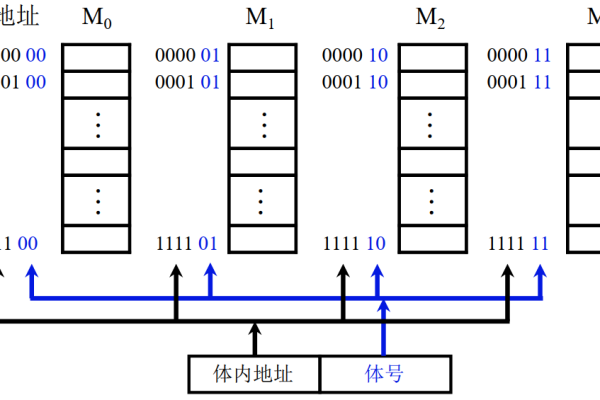

早期计算机系统的地址总线位数有限,若系统使用16位地址总线,最大寻址空间为64KB(2^16),但如果物理内存实际超过这一容量,可能导致不同逻辑地址映射到同一物理位置。内存映射策略

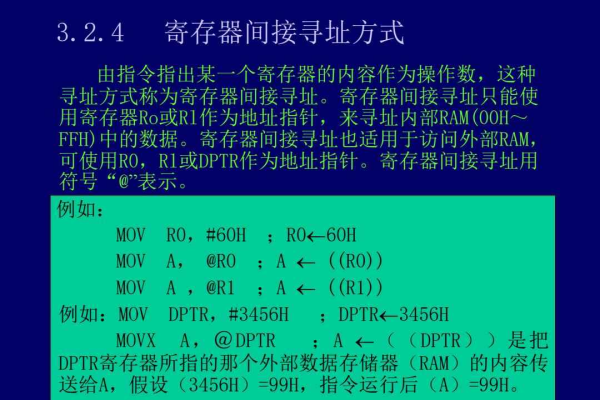

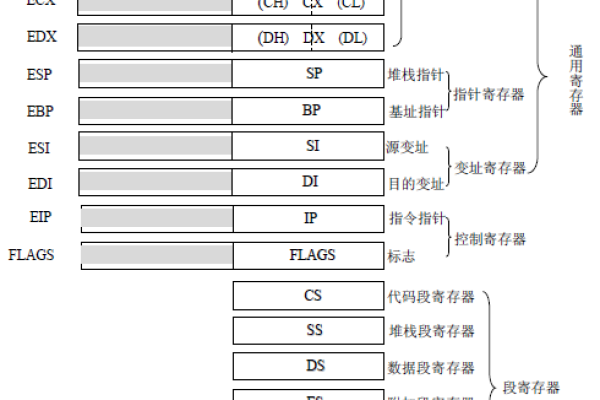

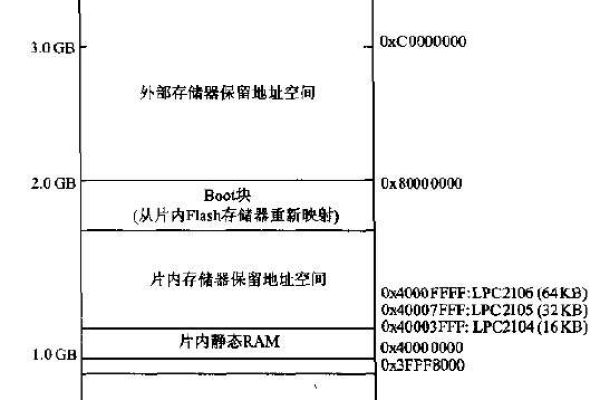

在嵌入式系统中,为了复用硬件资源(如I/O端口和内存),可能通过地址映射将不同功能区域分配到同一物理地址,若设计不当,可能引发意外的地址重叠。分段内存管理

x86架构的早期处理器(如8086)采用分段机制,逻辑地址由段基址和偏移量组成,段地址0x1000和偏移0x0001的组合可能指向与段地址0x0FFF和偏移0x0011相同的物理地址,导致重叠。

地址重叠会导致哪些问题?

数据冲突与覆盖

若两个程序或进程的地址映射到同一物理内存,一方的数据修改会直接影响另一方,导致程序崩溃或数据错误。

调试困难

地址重叠可能导致程序运行结果不可预测,且难以通过逻辑分析定位问题根源。资源浪费

系统可能因重叠而无法充分利用物理内存,降低整体性能。

如何解决存储器地址重叠?

改进地址解码电路

硬件层面可通过更精确的地址解码芯片(如74LS138)设计,确保每个逻辑地址唯一对应物理单元。引入内存管理单元(MMU)

现代处理器通过MMU实现虚拟地址到物理地址的动态映射,隔离不同进程的内存空间,操作系统使用页表(Page Table)管理映射关系,避免重叠。

系统级优化

- 固定地址分配:为关键硬件资源(如外设寄存器)预留专用地址空间。

- 动态地址分配:在程序运行时通过内存池(Memory Pool)或堆管理器动态分配地址,减少冲突风险。

开发工具辅助检测

使用调试器(如GDB)或内存检查工具(如Valgrind)扫描地址冲突,提前发现潜在问题。

实际案例

案例1:8086处理器的分段机制

8086的20位物理地址由16位段地址左移4位加上16位偏移地址生成,段地址0xFFFF和偏移0x0010会指向物理地址0x10000,但实际物理总线仅20位,导致地址回绕到0x0000,产生重叠。案例2:嵌入式系统中的I/O映射

某嵌入式设备将UART控制寄存器映射到地址0x4000,同时错误地将某段内存分配到同一地址,导致UART操作时意外改写内存数据。

现代系统中的应对

当前,操作系统(如Linux、Windows)通过虚拟内存管理和进程隔离机制,几乎消除了用户程序层面的地址重叠问题,但在裸机开发(如单片机)或驱动编程中仍需开发者手动管理,确保地址分配合理。

引用说明

- 《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)

- Intel 8086处理器手册

- 《操作系统概念》(Abraham Silberschatz, Peter Baer Galvin, Greg Gagne)

通过理解存储器地址重叠的原理与解决方案,开发者可以更高效地设计系统,避免潜在风险。