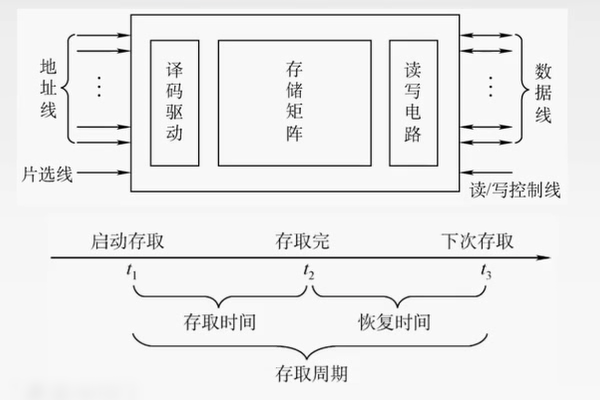

存储器读写过程

- 行业动态

- 2025-04-11

- 3

存储器读写过程包括寻址、数据传输和控制操作,读操作时,CPU通过地址总线定位存储单元,数据经数据总线传回;写操作则将数据与地址同时发送,由控制信号协调完成存储,时序同步与信号校验确保信息准确交互。

从原理到应用

在计算机系统中,存储器是承载数据存储与交换的核心组件,无论是运行程序、加载文件,还是执行日常操作,存储器的读写过程都直接影响系统性能与用户体验,以下将从RAM(随机存取存储器)和ROM(只读存储器)两类常见存储器入手,详解其读写机制与底层原理。

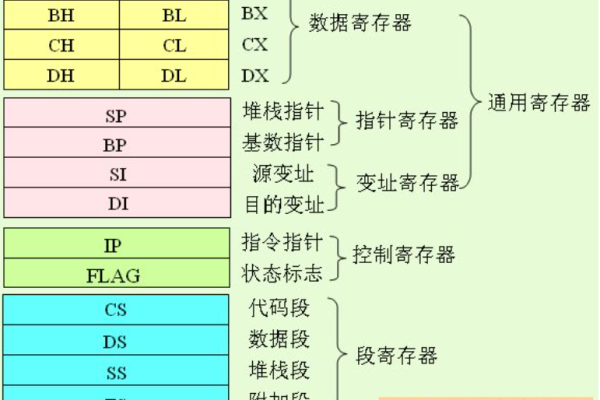

RAM的读写过程

RAM以DRAM(动态随机存取存储器)为例,其特点是需要周期性刷新以保持数据,广泛应用于内存条。

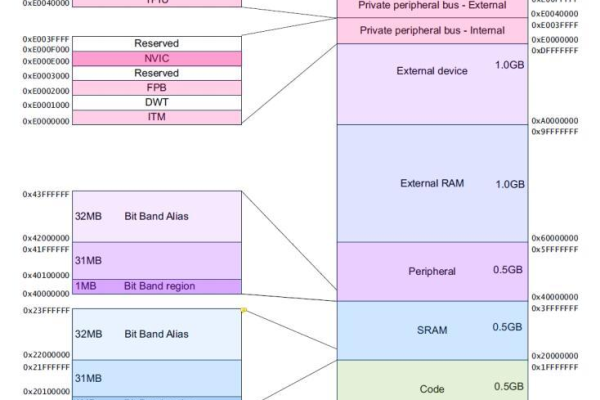

寻址阶段

- CPU通过地址总线发送目标数据的物理地址。

- 内存控制器将地址拆分为行地址(Row Address)与列地址(Column Address)。

- 行地址选中存储阵列中的特定行,将该行的所有存储单元(电容)电荷状态加载到“行缓冲区”。

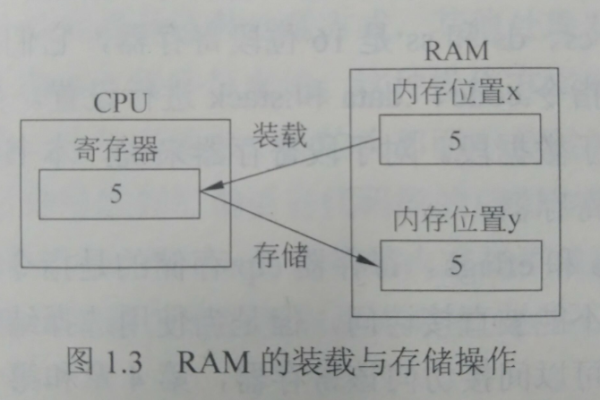

读取操作

- 列地址解码后选中目标存储单元。

- 感应放大器(Sense Amplifier)检测电容的电荷量:高电平代表“1”,低电平代表“0”。

- 数据通过数据总线传回CPU或缓存,同时原存储行因电荷被读取而需重新写入以保持数据。

写入操作

- CPU通过数据总线发送待写入的二进制数据。

- 行地址选中存储行后,列地址定位目标单元。

- 写入电路将电容充电(写入“1”)或放电(写入“0”),完成数据更新。

关键特性:

- 刷新机制:DRAM每隔64ms需对全部存储行刷新一次,防止电荷流失导致数据丢失。

- 延迟影响:行地址切换(Row Hammer)可能引起邻近行数据错误,需通过纠错码(ECC)缓解。

ROM的读写过程

以NAND闪存为例(常用于SSD、U盘),其特点为非易失性,但写入前需擦除。

存储单元结构

- 每个存储单元由浮栅晶体管(Floating Gate Transistor)构成。

- 浮栅捕获电子数量决定单元状态:高电子量为“0”,低电子量为“1”。

读取操作

- 控制器根据逻辑地址映射到物理块(Block)和页(Page)。

- 施加读取电压(如3V)至控制栅,检测源极-漏极电流。

- 电流大小反映浮栅电子量,从而判断存储的是“0”或“1”。

写入(编程)操作

- 写入前需对目标块执行擦除(Erase),将所有单元设为“1”(释放浮栅电子)。

- 施加高电压(约20V)至控制栅,迫使电子穿过绝缘层进入浮栅(写入“0”)。

- 数据以页(通常4KB)为单位写入,但擦除必须以块(如256页)为单位。

擦除限制

- 每个存储块的擦写次数有限(SLC约10万次,QLC约1千次),超过后可能永久损坏。

- 控制器通过磨损均衡(Wear Leveling)算法分散写入压力。

存储器读写性能的关键因素

时序控制

- RAM的CL值(CAS Latency)决定读取延迟,数值越低速度越快。

- 闪存的页缓存(Page Buffer)加速连续读取,但随机写入性能受制于擦除时间。

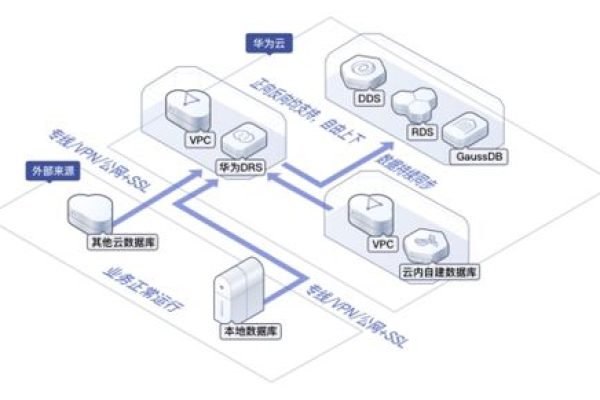

接口与协议

DDR4内存通过双倍数据速率提升带宽;NVMe协议优化SSD与CPU的直连效率。

纠错与冗余

ECC内存可修正单比特错误;闪存通过LDPC编码对抗电荷泄漏。

实际应用中的注意事项

- 内存兼容性:需匹配主板支持的频率与电压。

- SSD优化:保留至少10%的OP空间(Over-Provisioning)以延长寿命。

- 数据安全:突然断电可能导致DRAM数据丢失或闪存写入中断,需配置UPS电源。

引用说明

本文技术细节参考自《计算机体系结构:量化研究方法》(第6版)、JEDEC固态技术协会发布的DDR4标准,以及三星电子公开的V-NAND闪存技术白皮书。