存储器单元寻址原理

- 行业动态

- 2025-04-11

- 2

存储器单元寻址是通过地址总线传输二进制地址信号,由地址解码器确定唯一存储单元位置的过程,每个单元拥有独立地址,CPU根据地址访问对应存储位置进行数据读取或写入,实现数据的精准定位与操作,是计算机执行指令和管理数据的基础机制。

在计算机系统中,存储器单元寻址是数据存取的核心机制,理解这一原理不仅有助于认识计算机如何高效管理数据,还能为优化程序性能提供理论依据,以下是关于存储器寻址的详细解析:

存储器地址的基本概念

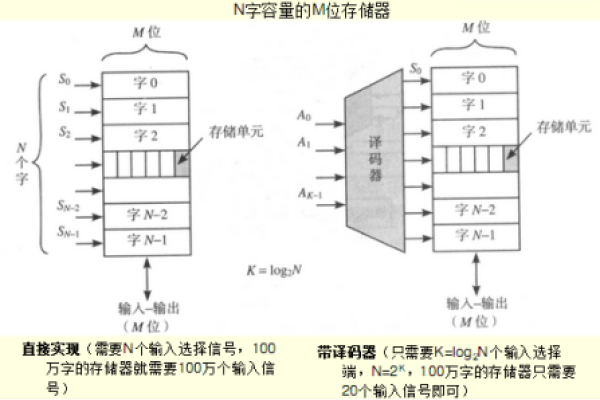

存储器由大量存储单元(Memory Cell)组成,每个单元可存储固定长度的数据(例如1字节),为了准确访问特定单元,系统为每个单元分配唯一的物理地址(Physical Address)。

- 地址总线的作用:CPU通过地址总线(Address Bus)传输目标单元的地址信号,地址总线的位数直接决定可寻址的内存空间大小,32位地址总线支持的最大寻址空间为 (2^{32} = 4 text{GB})。

- 地址解码器:存储器控制器接收到地址信号后,通过地址解码器将二进制地址转换为对应存储单元的物理位置,类似“门牌号”定位。

寻址机制的实现过程

存储器寻址包含以下关键步骤:

- 地址生成:CPU根据程序指令或数据需求生成目标地址。

- 地址传输:地址信号通过地址总线传输至存储控制器。

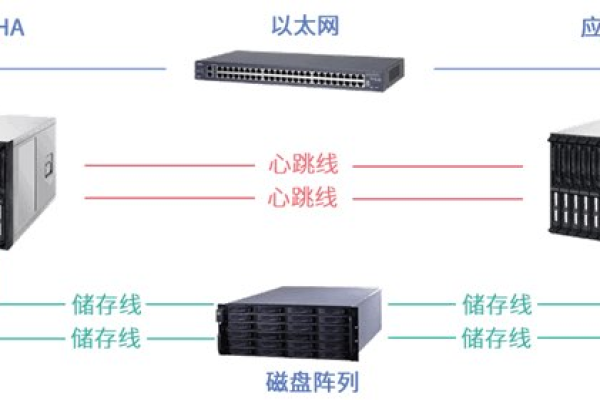

- 地址映射:控制器根据内存映射表(Memory Map)确定目标地址对应的物理存储位置(如RAM、ROM或I/O设备)。

- 数据读写:控制器激活对应存储单元,通过数据总线(Data Bus)完成数据输入或输出。

物理寻址与虚拟寻址的区别

物理寻址

- 直接访问硬件层面的存储单元地址。

- 适用于早期操作系统或嵌入式系统,缺乏内存保护机制。

虚拟寻址

- 通过内存管理单元(MMU)将程序使用的虚拟地址转换为物理地址。

- 支持内存隔离、分页机制和交换空间,提升安全性与资源利用率。

- 现代操作系统(如Windows、Linux)均采用虚拟内存管理。

存储器寻址的层级结构

为提高效率,计算机系统采用多级存储结构:

- 寄存器:CPU内部直接访问,速度最快,容量最小。

- 高速缓存(Cache):分为L1、L2、L3三级,通过局部性原理减少访问主存的延迟。

- 主存(RAM):由DRAM构成,容量较大但速度较慢,通过地址总线和控制器管理。

- 辅助存储器:如硬盘、SSD,通过I/O接口映射为内存地址空间。

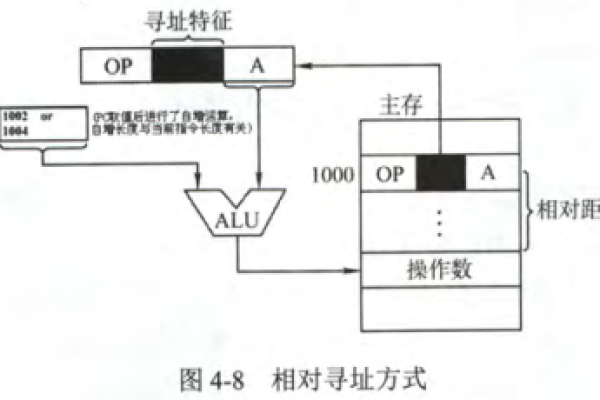

常见寻址模式

- 直接寻址:指令中直接给出存储单元地址。

- 示例:

MOV AX, [0x1234](读取地址0x1234的数据到AX寄存器)。

- 示例:

- 间接寻址:指令中给出存放地址的寄存器。

- 示例:

MOV AX, [BX](读取BX寄存器指向地址的数据)。

- 示例:

- 基址变址寻址:结合基址寄存器和偏移量计算地址。

- 示例:

MOV AX, [BX+SI+0x10](地址= BX + SI + 0x10)。

- 示例:

寻址技术的演进与挑战

- 内存扩展技术:如Bank Switching(存储体切换)突破地址总线限制。

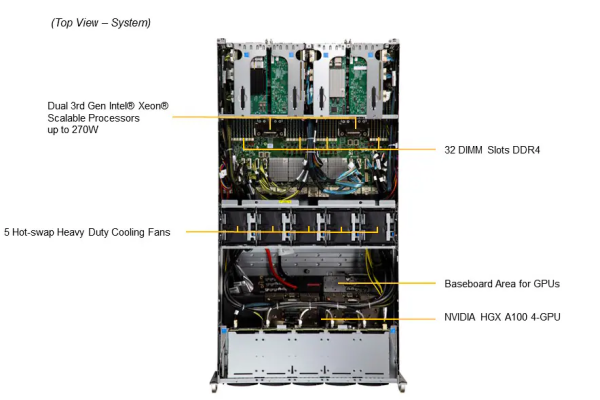

- 多通道架构:DDR SDRAM通过双通道或四通道提升带宽。

- 非易失性内存:如NVM(非易失性内存)的寻址方式与传统DRAM存在差异,需适配新的控制器逻辑。

寻址错误与调试

- 地址越界:访问未分配的内存区域会导致程序崩溃(如Segmentation Fault)。

- 对齐问题:未按内存对齐要求访问数据可能降低性能或触发异常。

- 调试工具:GDB、Valgrind等工具可检测内存地址错误。

引用说明

- 《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)

- JEDEC标准文档(JESD79-4B, DDR4 SDRAM规范)

- Intel® 64 and IA-32 Architectures Software Developer Manuals

- RFC 1180:TCP/IP协议中对内存寻址的早期实现描述

通过理解存储器寻址原理,开发者可以更高效地管理内存资源,而硬件工程师能够设计出性能更强的存储架构,无论是编程优化还是系统设计,这一基础理论都起着决定性作用。