存储器ram能直接与cpu 交换信息

- 行业动态

- 2025-04-11

- 2

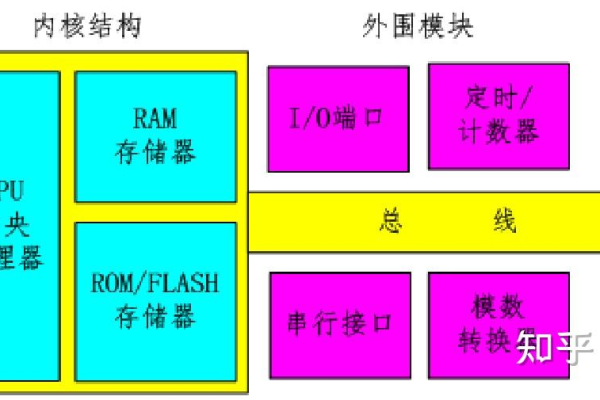

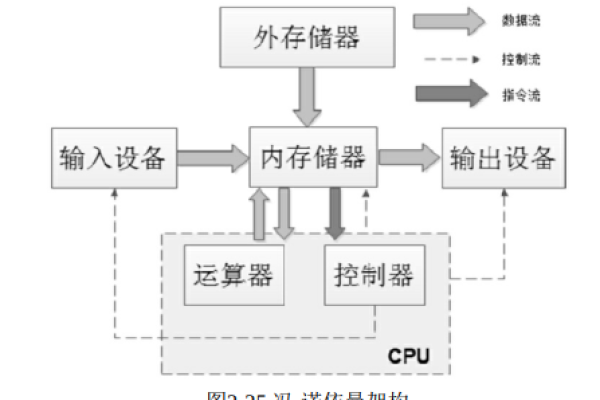

在计算机体系结构中,随机存取存储器(RAM)与中央处理器(CPU)的交互是系统高效运行的核心机制之一,RAM作为临时数据存储介质,能够直接与CPU交换信息,这一过程直接影响着计算机的运算速度与整体性能,以下是这一机制的技术解析与实现原理。

RAM与CPU的直接交互机制

物理连接与通信通道

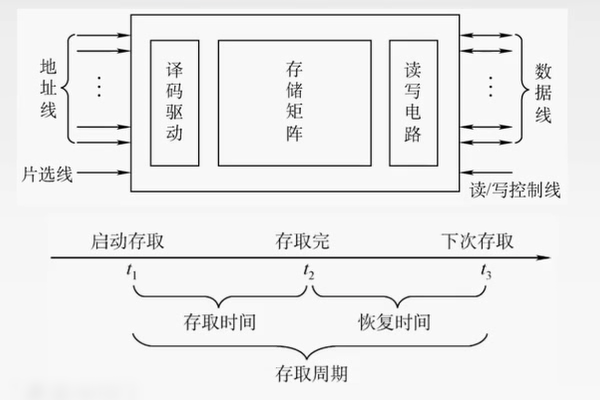

CPU通过内存控制器(Memory Controller)与RAM建立物理连接,这种连接依赖于三类总线:- 地址总线(Address Bus):传递CPU需要访问的内存地址。

- 数据总线(Data Bus):传输CPU与RAM之间交换的实际数据。

- 控制总线(Control Bus):发送读写信号、时钟同步等指令。

当CPU需要读取或写入数据时,内存控制器会将请求转化为电信号,通过总线发送至RAM的指定位置,整个过程通常在纳秒级别完成。

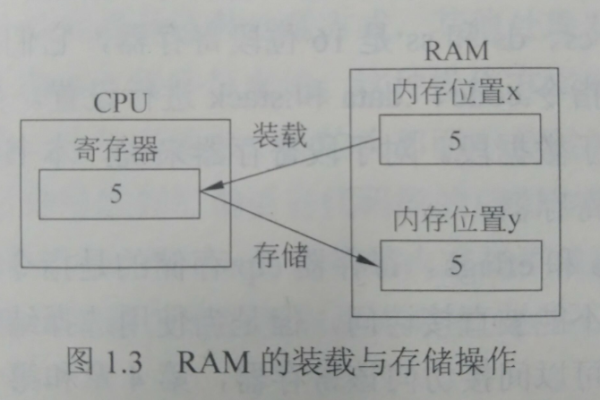

读写操作的实现

- 读取数据:CPU发送目标地址至RAM,RAM定位对应存储单元后,将数据通过数据总线返回CPU。

- 写入数据:CPU将目标地址和数据同时发送至RAM,RAM将数据存储到指定位置。

这一过程依赖于时钟信号的同步,确保每一步操作按严格时序执行。

缓存(Cache)的辅助作用

虽然RAM与CPU可直接通信,但现代CPU通过多级缓存(L1/L2/L3 Cache)进一步优化性能,缓存作为临时高速存储区,保存CPU频繁访问的数据副本,减少直接访问RAM的延迟,缓存的存在并不改变RAM与CPU直接交互的本质逻辑。

为何RAM能实现“直接交换”?

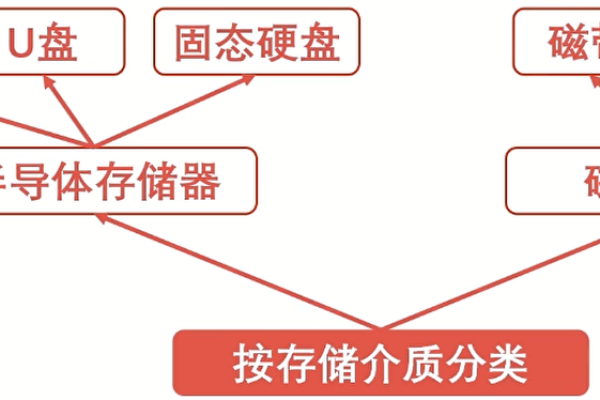

存储介质的物理特性

RAM基于半导体技术,支持随机访问(Random Access),即CPU可通过地址直接定位任意存储单元,无需顺序遍历,这与硬盘等顺序存储设备有本质区别。内存控制器的桥梁作用

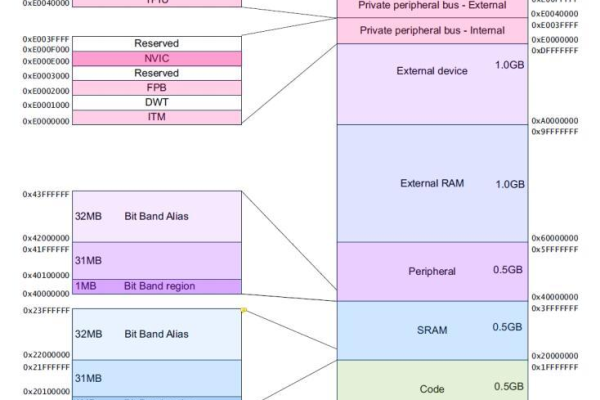

内存控制器集成于CPU或主板芯片组中,负责翻译CPU指令、管理总线通信,并协调RAM的读写时序,Intel处理器的集成内存控制器(IMC)支持DDR4/DDR5协议,显著提升了数据传输效率。

同步动态RAM(SDRAM)的技术支持

现代RAM多采用SDRAM技术,其工作频率与CPU时钟同步,例如DDR5内存的数据传输速率可达6400 MT/s以上,高带宽与低延迟特性使其能够满足CPU的实时数据需求。

性能瓶颈与优化方向

尽管RAM与CPU直接通信,但两者速度差异可能成为瓶颈:

- 速度不匹配:CPU的运算速度远高于RAM响应时间,解决方案包括增大缓存容量、采用更快的存储技术(如HBM显存)。

- 并行访问优化:通过双通道、四通道内存配置,提升总带宽。

- 预取技术:CPU预测未来需要的数据并提前加载至缓存,减少等待时间。

权威验证与行业标准

根据《计算机组成与设计:硬件/软件接口》(David A. Patterson, John L. Hennessy)的阐述,CPU与RAM的交互是冯·诺依曼架构的核心环节,内存控制器的设计直接决定了系统效率,JEDEC(固态技术协会)制定的DDR标准规范了RAM与CPU的通信协议,确保兼容性与性能提升。

通过上述机制,RAM与CPU的紧密协作支撑了计算机的实时数据处理能力,理解这一过程,有助于优化硬件配置、诊断性能问题,并为未来技术演进(如非易失性内存)奠定基础。

引用说明:

- Patterson, D. A., & Hennessy, J. L. Computer Organization and Design: The Hardware/Software Interface.

- JEDEC固态技术协会. DDR5 SDRAM标准.

- Intel白皮书. 集成内存控制器技术解析.