存储器数据cache

- 行业动态

- 2025-04-11

- 2

数据Cache是位于CPU与主存间的高速缓存,用于减少处理器访问

数据的延迟,它基于局部性原理,存储近期使用的数据副本,通过快速响应高频访问提升系统性能,采用多级结构(L1/L2/L3)分级管理,配合替换算法(如LRU)和写策略(直写/回写)维持数据一致性,显著提高内存访问效率和CPU利用率。

在计算机系统中,存储器数据Cache(高速缓存)是一个至关重要的组件,它通过优化数据访问速度,显著提升了系统性能,无论是个人电脑、智能手机还是云计算服务器,Cache的设计直接影响着数据处理效率和用户体验,以下从技术原理、实际应用及优化策略等方面展开解析。

什么是数据Cache?

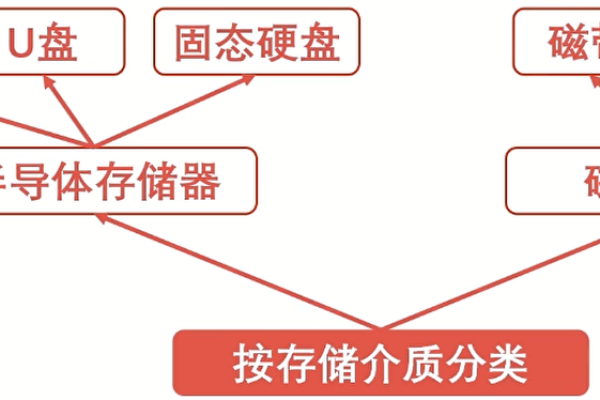

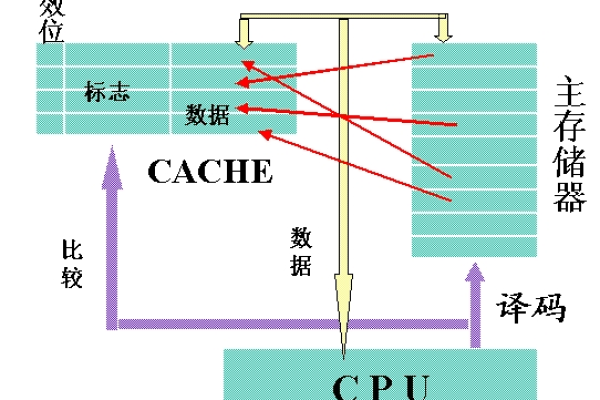

数据Cache是一种临时存储介质,位于CPU核心与主存(如内存)之间,用于缓存频繁访问的数据或指令,其核心目标是减少CPU访问主存的延迟(Latency),通过空间局部性(Spatial Locality)和时间局部性(Temporal Locality)原理,将热点数据存储在更靠近处理器的位置。

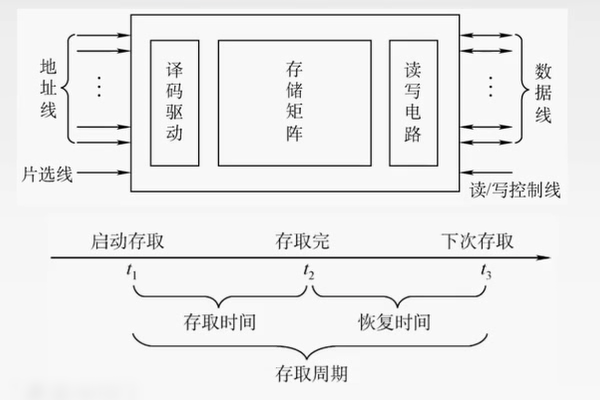

关键技术指标:

- 命中率(Hit Rate):CPU所需数据在Cache中找到的比例,直接影响性能。

- 访问时间(Access Time):Cache读取数据的速度,通常为纳秒级。

- 容量与关联度:Cache大小和映射策略(如直接映射、组相联映射)决定存储效率。

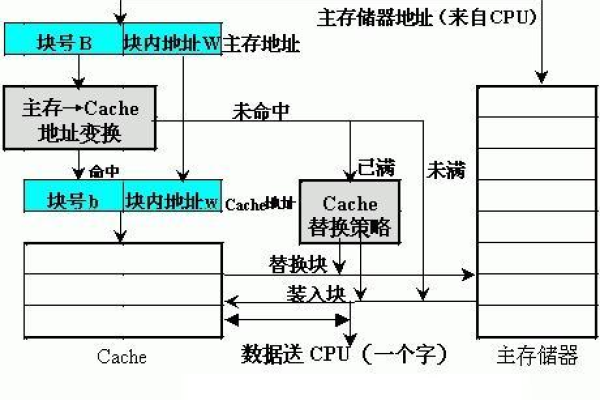

Cache如何工作?

数据缓存流程

当CPU请求数据时,系统按以下顺序查找:

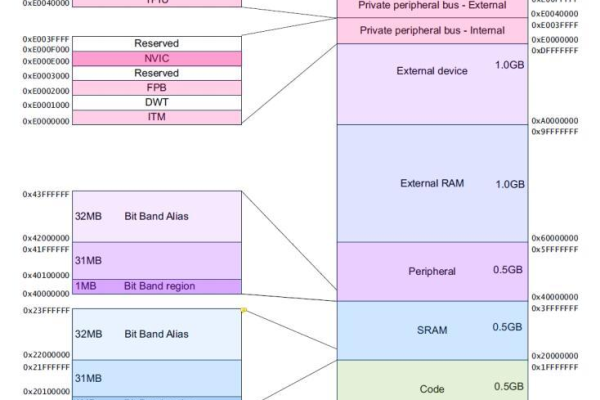

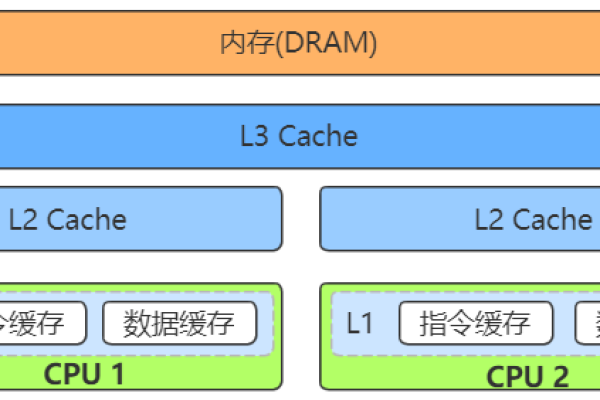

1️⃣ L1 Cache(一级缓存):速度最快(约1-3个时钟周期),容量最小(通常KB级);

2️⃣ L2/L3 Cache:容量更大(MB级),速度次之;

3️⃣ 主存(RAM):若Cache未命中,需从内存加载数据,耗时增加百倍以上。

映射策略

- 直接映射(Direct Mapped):每个主存块仅能映射到Cache的固定位置;

- 全相联映射(Fully Associative):数据可存入任意Cache位置,但搜索复杂度高;

- 组相联映射(Set Associative):折中方案,将Cache分为多个组,提升灵活性。

替换算法

当Cache已满时,需选择淘汰策略:

- LRU(最近最少使用):优先替换最久未访问的数据;

- FIFO(先进先出):按进入顺序淘汰;

- 随机替换:实现简单但效率较低。

数据Cache的实际价值

性能提升

- 普通CPU的L1 Cache访问延迟约为1ns,而主存访问延迟可达100ns,通过高命中率的Cache设计,可减少70%以上的内存访问时间。

- 案例:Intel Core i9处理器的三级缓存(L3)达到24MB,支持多核共享,显著提升多线程任务效率。

能耗优化

Cache命中时,CPU无需启动高功耗的内存控制器,可降低整体功耗,移动设备(如智能手机)依赖此特性延长续航。

应用场景

- 数据库系统:通过缓存热点查询结果,减少磁盘I/O;

- GPU渲染:纹理缓存加速图形处理;

- Web服务器分发网络(CDN)本质上是分布式Cache。

Cache设计的挑战与趋势

技术瓶颈

- 容量与速度的权衡:SRAM(Cache常用材料)密度低,大容量Cache成本高昂;

- 一致性协议:多核CPU中需通过MESI协议维护Cache一致性,增加设计复杂度。

创新方向

- 非易失性Cache:采用STT-MRAM等技术,断电后保留数据;

- 机器学习预取:通过AI预测数据访问模式,主动加载至Cache;

- 3D堆叠封装:如AMD的3D V-Cache,垂直堆叠提升容量密度。

如何优化Cache利用率?

- 代码层面:优化数据访问模式(如循环遍历顺序),增强局部性;

- 硬件配置:选择高关联度Cache的处理器(如8-way Set Associative);

- 工具分析:使用Valgrind、Perf等工具分析Cache Miss热点。

引用说明

- Hennessy, J. L., & Patterson, D. A. (2017). 计算机体系结构:量化研究方法(第6版). 机械工业出版社.

- Intel Corporation. (2022). 第12代酷睿处理器技术白皮书.

- ARM Limited. (2021). Cortex-A78 CPU技术参考手册.