存储器实验 数据流向图

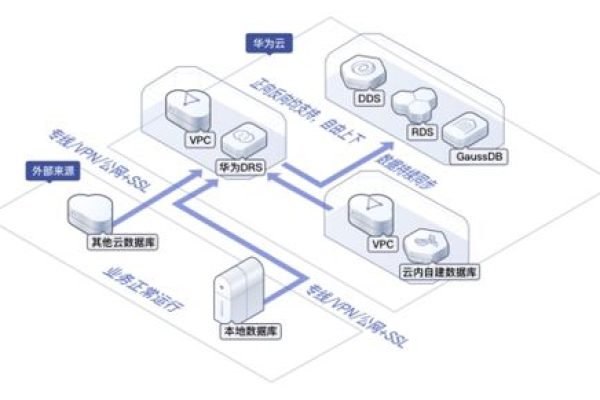

- 行业动态

- 2025-04-11

- 3

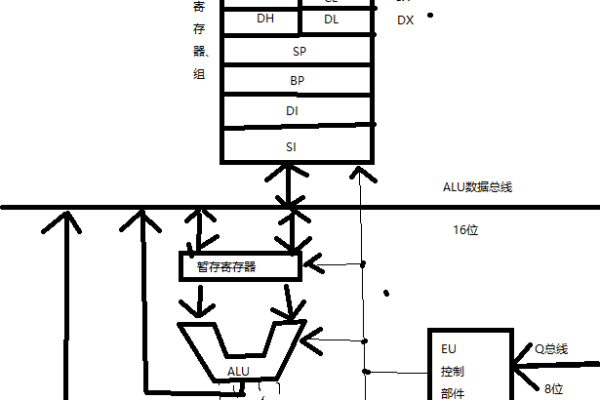

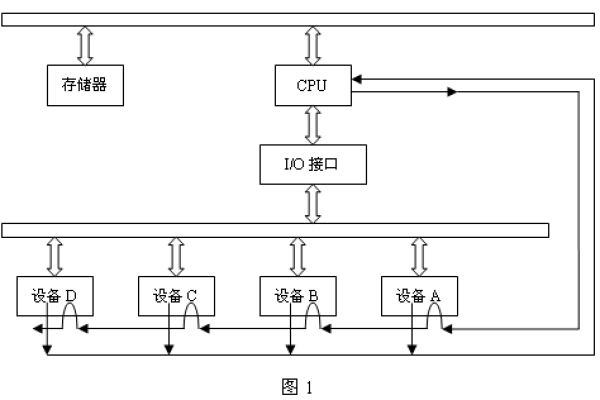

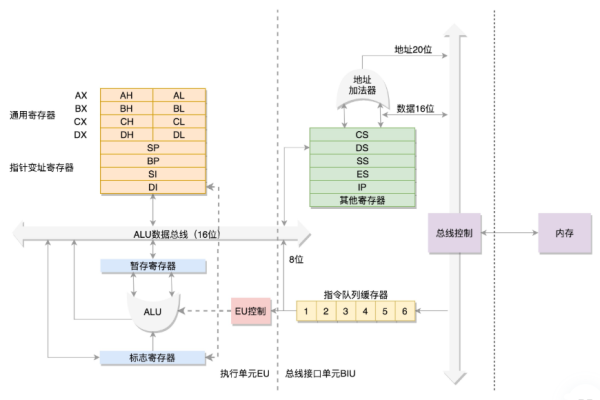

存储器实验数据流向图展示了数据在寄存器、内存单元与总线间的传输路径,通过控制信号协调,数据从输入设备经总线暂存至缓冲寄存器,由存储体地址译码定位后完成读写操作,输出时通过总线返回显示设备,直观呈现存储访问过程中地址选择、信号传递与数据流动的时序关系。

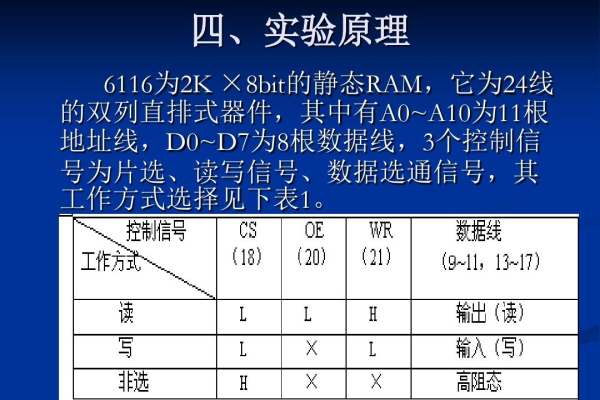

存储器实验中的数据流向图解析

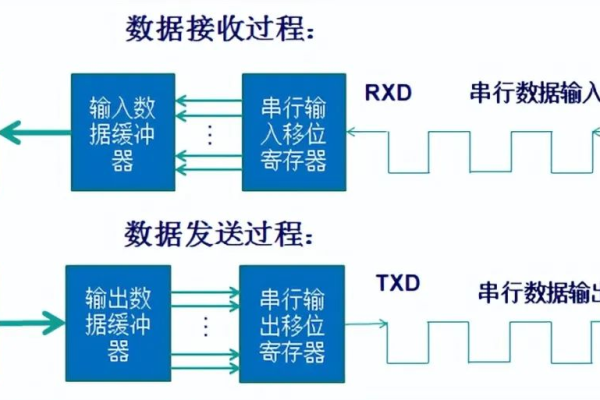

在计算机组成与数字电路实验中,存储器实验是理解硬件数据交互的核心环节,而数据流向图作为可视化工具,能够清晰展示数据在存储器、总线、控制器之间的传输路径,本文从实验原理、流程拆解、绘制方法等角度,系统解析数据流向图的设计与应用。

存储器实验的基本组成

存储器实验通常由以下硬件构成:

- 存储单元:如RAM、ROM芯片,负责数据存储;

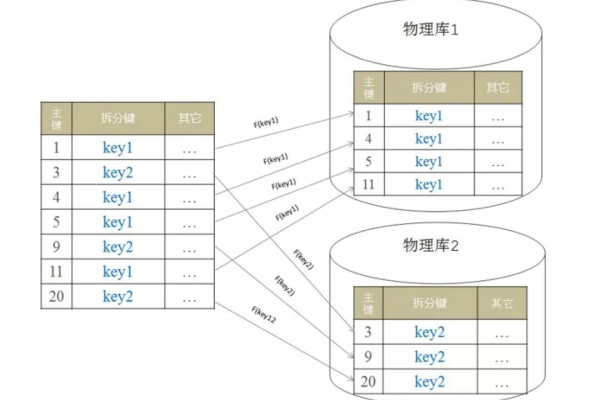

- 地址总线:传递CPU或控制器发送的地址信号;

- 数据总线:双向传输读写数据;

- 控制总线:发送读写使能(Read/Write Enable)、片选(Chip Select)等信号;

- 时钟模块:同步各部件操作时序。

数据流向图的核心作用

- 可视化操作流程:明确读写操作中数据的来源、传输路径及终点;

- 排查硬件错误:通过逻辑验证,定位总线冲突或时序问题;

- 优化系统设计:分析延迟瓶颈,提升存储器访问效率。

典型数据流向场景拆解

数据写入存储器

- 地址传输

CPU通过地址总线发送目标存储地址(如0x0010)至存储器。 - 控制信号激活

控制总线发送Write Enable和Chip Select信号,通知存储器进入写入状态。 - 数据传输

待写入数据(如8位二进制数10101100)通过数据总线传输至存储器指定地址。

数据从存储器读取

- 地址锁定

CPU向地址总线发送读取地址(如0x0020)。 - 读信号触发

控制总线发送Read Enable,存储器将对应地址数据输出至数据总线。 - 数据回传

数据总线将值传输至CPU或外部寄存器。

如何绘制数据流向图

- 标注核心组件

用矩形框表示CPU、存储器、总线,并标注型号(如SRAM 62256)。

[CPU] ---地址总线---> [存储器] <---数据总线---> ---控制总线---> - 箭头表示流向

- 单箭头:单方向传输(如地址总线);

- 双箭头:双向传输(如数据总线)。

- 添加信号标注

在控制总线旁标注WE(写使能)、OE(输出使能)等信号状态(如高电平/低电平有效)。 - 时序同步标记

用波浪线或时间轴注明时钟周期(如T1~T4阶段的信号变化)。

实验常见问题与数据流向分析

- 问题1:写入数据与读取结果不一致

⇒ 检查数据总线是否在写入阶段被其他设备占用(如未关闭其他芯片的OE信号)。 - 问题2:地址无法锁定

⇒ 验证地址总线连接是否断路,或控制信号时序是否滞后于地址传输。

数据流向图通过图形化呈现,将抽象的存储器操作转化为直观的逻辑链路,是硬件调试与优化的关键工具,掌握其绘制方法,可快速定位实验故障,并深化对计算机存储体系的理解。

参考文献

- Patterson, D. A., & Hennessy, J. L. (2017). 《计算机组成与设计:硬件/软件接口》. 机械工业出版社.

- Intel. (1994). Memory Component Data Book. 官方技术手册.

- University of Cambridge. (2020). Digital System Design Lab Guides. 实验指导文档.