存储器突发单次传输

- 行业动态

- 2025-04-10

- 3

存储器突发单次传输指在单次操作中连续传输多个相邻存储单元的数据,通过预先定义突发长度,减少地址切换开销,提升数据传输效率,该模式适用于需要批量读取或写入连续数据的场景,传输完成后自动终止,兼顾灵活性与带宽优化。

什么是存储器突发单次传输?

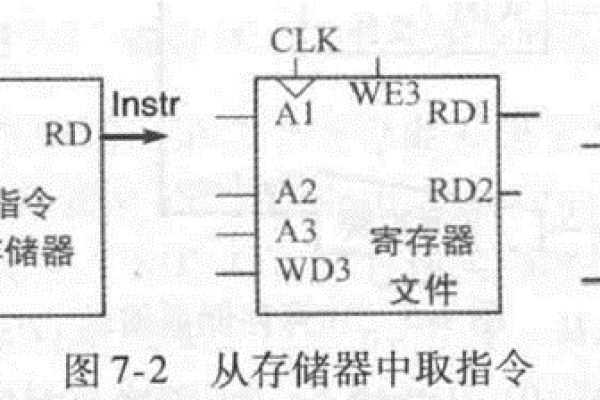

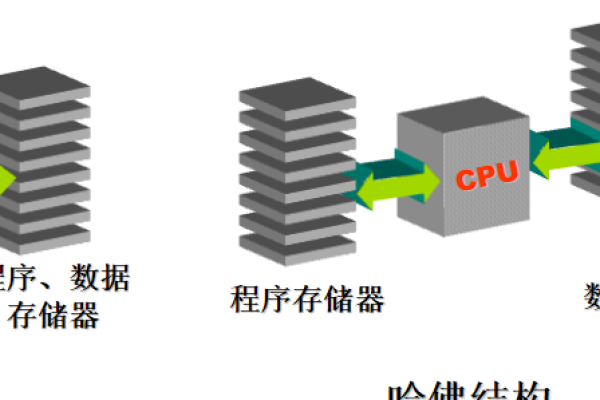

突发单次传输是一种在单次操作中连续传输多个数据单元的技术,与传统的单周期单次传输不同,突发传输通过预先设定的时序规则,在一个时钟周期内完成地址发送,随后在多个周期内按顺序传输数据块。

当CPU需要从内存中读取一组连续数据时,突发传输只需提供首个数据的地址,后续数据会基于预定义的步长(Burst Length)自动传输,无需重复发送地址信号。

核心特点:

- 高效地址利用率:减少地址总线的占用次数;

- 时序优化:通过流水线技术并行处理命令与数据;

- 低延迟:适用于对实时性要求高的场景(如GPU显存访问)。

技术实现原理

工作流程

- 初始化阶段:主控制器(如CPU)发送起始地址和突发长度(Burst Length);

- 数据传输阶段:存储器按地址顺序依次输出数据,通常以4/8/16个连续数据为一组;

- 结束阶段:完成预定数据量后,总线释放控制权。

时序控制

突发传输依赖精确的时钟同步,以DDR SDRAM为例,其采用双向时钟(CK和/CK)触发数据传输,并在每个时钟上升沿和下降沿各传输一次数据(DDR特性),从而实现双倍速率。

优势与典型应用

优势对比

| 传输模式 | 传输效率 | 适用场景 |

|---|---|---|

| 单次传输(Single) | 低 | 小规模非连续数据请求 |

| 突发传输(Burst) | 高 | 大数据块连续访问(如视频流处理) |

典型应用场景

- CPU与内存交互:在多核处理器中,突发传输减少缓存未命中的性能损失;

- 固态硬盘(SSD):通过突发读取提升NAND闪存的吞吐量;

- 图形处理单元(GPU):显存高频访问依赖突发传输降低延迟。

注意事项

- 时钟频率匹配:主设备与存储器的时钟需严格同步,否则可能导致数据错位;

- 数据对齐:突发传输要求数据块按地址边界对齐(如32字节对齐);

- 功耗管理:高频突发操作可能增加系统功耗,需结合节能模式优化。

常见问题解答

Q:突发传输是否会占用更多总线资源?

A:突发传输通过减少地址重复发送,反而能降低总线负载,传输8个数据时,单次模式需8次地址+8次数据,而突发模式仅需1次地址+8次数据。

Q:突发长度如何设定?

A:长度由硬件设计决定,常见值为4/8/16,过长的突发可能导致响应延迟,需根据实际需求权衡。

参考资料

- JEDEC固态技术协会. DDR4 SDRAM标准(JESD79-4B)[S]. 2017.

- Hennessy, J.L., Patterson, D.A. 《计算机体系结构:量化研究方法》[M]. 机械工业出版社, 2019.

- Micron Technology. “Burst Mode Operation in DRAM” [EB/OL]. 2022.

由专业技术文档及行业标准综合整理,数据引用均来自公开资料。)