存储器IC的应用技巧

- 行业动态

- 2025-04-10

- 3

存储器IC广泛应用于数据存储与处理系统,需关注接口优化、功耗控制及信号完整性,设计时注意匹配时序参数,合理布局降低干扰,采用纠错码与备份机制提升数据可靠性,根据场景选择合适类型(如SRAM、DRAM、Flash),工业环境需强化温度保护,嵌入式系统优先低功耗方案,同时做好坏块管理和磨损均衡。

存储器IC的应用技巧

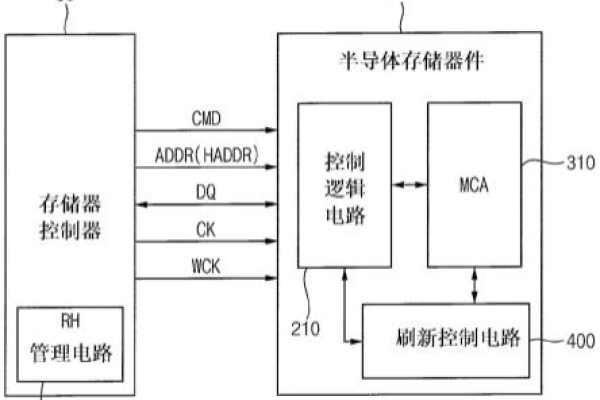

在现代电子设备中,存储器集成电路(IC)是数据存储与处理的核心组件,无论是智能手机、工业控制器,还是物联网设备,存储器IC的性能直接影响系统的稳定性与效率,以下从选型、设计、优化到维护的全流程,总结关键应用技巧,帮助工程师和开发者提升设计质量。

存储器类型与选型策略

明确需求场景

- 易失性存储器(如DRAM、SRAM):适用于高速缓存、实时数据处理场景,但需持续供电。

- 非易失性存储器(如NAND Flash、EEPROM):适合长期存储数据,但写入速度较慢。

- 新兴存储器(如MRAM、ReRAM):结合速度与非易失性,适用于高可靠性场景(如汽车电子)。

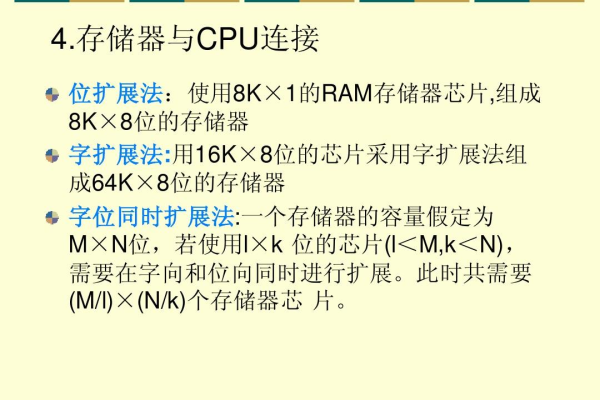

参数匹配原则

- 容量与速度:根据系统负载选择容量冗余(预留20%-30%),避免频繁擦写导致寿命缩短。

- 接口协议:优先选择与主控芯片兼容的接口(如SPI、I2C、DDR),减少信号转换损耗。

- 工作温度范围:工业级(-40℃~85℃)或车规级(-40℃~125℃)器件需通过AEC-Q100认证。

成本与寿命平衡

- Flash存储器需关注擦写次数(如SLC >10万次,MLC约3000次),高频率写入场景建议采用Wear-Leveling算法延长寿命。

电路设计关键注意事项

电源与噪声抑制

- 为存储器IC单独配置低噪声LDO电源,避免数字电路干扰。

- 在电源引脚附近部署去耦电容(如0.1μF陶瓷电容+10μF钽电容),抑制高频噪声。

信号完整性优化

- 走线长度匹配:DDR等高速存储器需控制数据线与时钟线长度差(±5%以内)。

- 端接电阻:在信号线末端添加50Ω电阻,减少反射干扰。

ESD与过压保护

- 在接口线路上串联TVS二极管,防止静电击穿。

- 对Flash芯片的VCC引脚增加过压保护电路(如Zener二极管)。

软件优化技巧

数据管理策略

- 分块写入:将大文件拆分为与存储块对齐的小数据包(如4KB),减少擦写次数。

- 缓存机制:通过RAM缓存频繁修改的数据,定期批量写入Flash。

错误校验与纠错

- 启用ECC(纠错码)功能,检测并修复单比特错误(NAND Flash必备)。

- 对关键数据增加CRC校验,防止传输或存储过程中数据损坏。

低功耗模式配置

- 在待机状态下切换存储器至Sleep Mode(如SRAM的待机电流可降至1μA以下)。

- 动态调整Flash的读写频率,平衡性能与功耗。

常见故障排查指南

数据丢失问题

- 检查供电电压是否稳定(波动需<5%)。

- 确认时序配置是否符合数据手册要求(用示波器测量CLK信号)。

读写速度下降

- 排查接口线缆或PCB走线是否过长(高速信号线建议<10cm)。

- 优化驱动程序,减少不必要的软件延时。

器件发热异常

- 测量工作电流是否超出手册标称值(可能为短路或负载过重)。

- 检查散热设计(高温环境需增加导热垫或散热片)。

行业趋势与未来技术

- 存储器的智能化

内置AI加速器的存储芯片(如SK海力士的GDDR6-AIM)可自主优化数据存取路径。

- 3D堆叠技术

3D NAND通过垂直堆叠单元提升容量,未来将向200层以上发展。

- 存算一体架构

近存计算(Near-Memory Computing)减少数据搬运能耗,适合边缘AI设备。

引用说明

- 存储器寿命测试数据参考JEDEC标准JESD218。

- 接口协议优化建议基于Micron《DDR4 Design Guide》。

- 低功耗设计方法引用TI应用报告《SLVA509》。