如何安全地进行BIOS降级操作?有哪些注意事项?

- 行业动态

- 2024-11-01

- 6

BIOS(Basic Input/Output System)是计算机主板上的一个固件,负责在计算机启动时进行硬件初始化和系统引导,用户可能需要将BIOS降级到旧版本,以解决新版本BIOS带来的兼容性问题、性能下降或特定功能缺失等问题,以下是关于BIOS降级的详细步骤和注意事项:

一、准备工作

1、备份重要数据:降级BIOS可能会导致数据丢失的风险,因此备份是非常重要的。

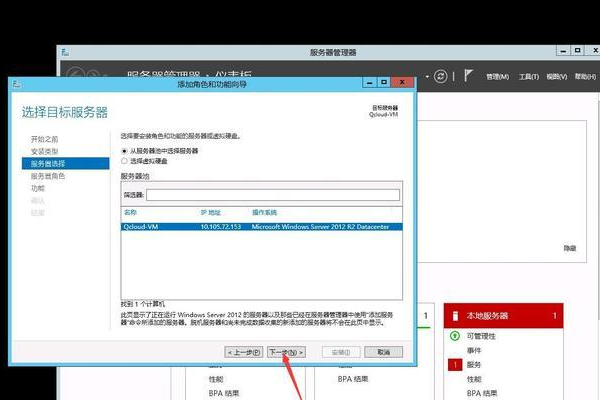

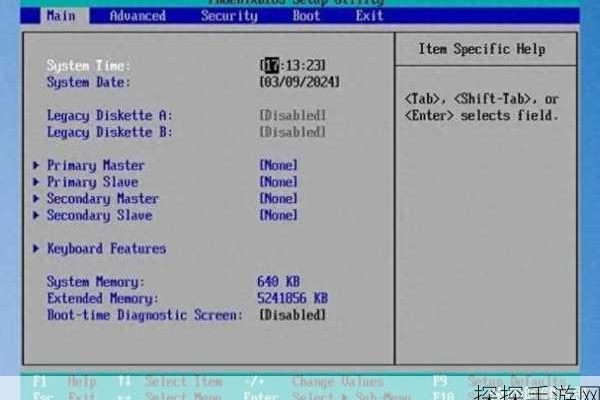

2、确认当前BIOS版本:在开始降级之前,需要确认当前计算机使用的BIOS版本。

3、查找旧版本BIOS文件:需要找到适用于计算机型号的旧版本BIOS文件,这可以通过访问官方网站或者联系客服来获取。

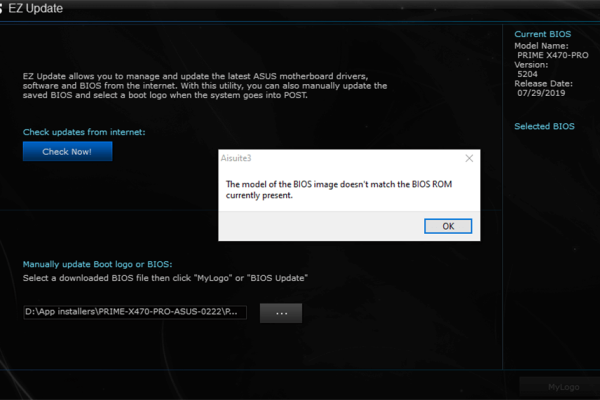

4、准备工具:根据不同的主板品牌,可能需要使用不同的工具,华硕主板可以使用自带的EasyFlash工具或第三方工具如winflash,其他品牌如戴尔、技嘉等,也可能需要特定的工具或方法。

二、降级步骤(以华硕主板为例)

1、下载并解压BIOS文件:从华硕官网下载所需降级的BIOS版本,并将其解压到硬盘或U盘的根目录下。

2、进入BIOS设置界面:将电脑关机,然后重新启动,在开机出现ASUS标志时,不断地按F4键以进入EasyFlash界面。

3、选择BIOS文件:在EasyFlash界面中,使用方向键选择存放BIOS文件的分区,并回车进入该分区目录,通过方向键选择之前下载并解压好的BIOS文件,点击回车键确认。

4、确认刷新:会跳出一个刷新确认窗口,通过方向键选择“Yes”并回车确认,开始刷新BIOS。

5、等待刷新完成:在刷新过程中,请确保电脑连接稳定的电源,并避免任何中断操作。

6、重启并检查:刷新成功后,笔记本会自动关机重启,重启后,可以进入BIOS界面确认BIOS版本是否已经成功降级。

三、注意事项与风险

1、确保选择正确的BIOS文件:降级前请务必确认选择的是正确的BIOS文件,以免出现问题。

2、避免中断降级过程:在降级过程中,请不要关闭电脑或中断降级过程,以免造成严重的损坏。

3、了解潜在风险:BIOS降级操作具有一定风险性,如果操作不当或遇到意外情况,可能导致电脑无法启动或硬件故障。

4、谨慎使用第三方工具:如果使用第三方工具进行降级,需要更加谨慎,因为不当的操作可能导致系统损坏或数据丢失。

四、常见问题解答

Q1: 为什么需要降级BIOS?

A1: BIOS降级通常是为了解决新版本BIOS带来的兼容性问题、性能下降或特定功能缺失等问题。

Q2: 如何知道哪个版本的BIOS最适合我的电脑?

A2: 可以根据电脑出厂时带的版本来判断,因为这个版本基本上是最稳定的,也可以通过网上搜索或咨询专业人士来获取更多信息。

Q3: 如果降级失败怎么办?

A3: 如果降级失败导致电脑无法启动,可以尝试使用恢复光盘或U盘启动电脑,并进行BIOS恢复操作,但请注意,这种方法并不总是有效,且存在一定风险。

BIOS降级是一项需要谨慎操作的任务,在进行降级之前,请务必备份重要数据并了解整个操作过程,如果不确定如何进行操作,建议寻求专业人士的帮助以避免潜在的风险。