如何在CentOS上安装和配置SSL证书?

- 行业动态

- 2024-12-04

- 5

在CentOS系统中配置SSL证书,特别是针对Tomcat服务器,是确保数据传输安全性的关键步骤,以下是详细的操作指南:

一、环境准备与前提条件

1、操作系统:CentOS 7.6 64位。

2、Web服务器:Tomcat 8.5或9。

3、JDK环境:提前安装并配置好,具体配置请参考Tomcat官网推荐的JDK兼容配置。

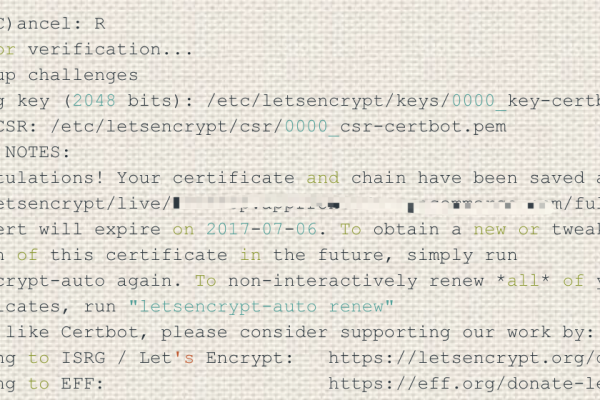

4、SSL证书:已通过数字证书管理服务控制台签发,并完成DNS解析(域名与IP地址映射)。

5、端口开放:确保Web服务器的443端口(HTTPS通信的标准端口)已开放。

二、下载SSL证书

1、登录数字证书管理服务控制台。

2、在左侧导航栏选择“证书管理 > SSL证书管理”。

3、定位到目标证书,点击“更多”后选择“下载”。

4、根据服务器类型(如Tomcat),点击下载并解压缩证书文件包。

三、在Tomcat服务器上安装证书

1、上传证书文件:将解压后的证书文件和密码文件上传到Tomcat服务器的conf目录,可以使用远程登录工具(如PuTTY、Xshell或WinSCP)进行上传。

2、配置server.xml:进入Tomcat安装根目录,打开server.xml文件进行编辑。

找到<Connector port="80" ... />配置项,修改redirectPort为443。

添加或修改443端口的Connector配置,启用SSL并指定证书文件路径及密码。

示例配置如下:

<Connector port="443" protocol="org.apache.coyote.http11.Http11NioProtocol"

maxThreads="150" SSLEnabled="true">

<SSLHostConfig>

<Certificate certificateKeystoreFile="conf/xxx.pfx"

certificateKeystorePassword="xxxxxx" type="RSA"/>

</SSLHostConfig>

</Connector>

3、可选配置:在conf/web.xml文件中添加配置项,实现HTTP请求自动跳转HTTPS。

4、重启Tomcat:执行以下命令停止并重启Tomcat服务。

./shutdown.sh #停止Tomcat服务 ./startup.sh #重启Tomcat服务

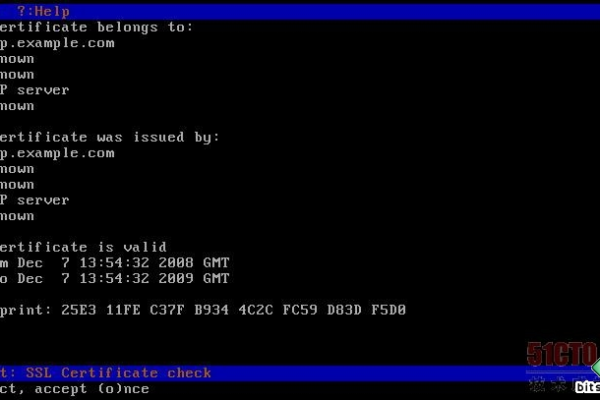

四、验证SSL证书是否安装成功

可以通过访问https://yourdomain.com来验证SSL证书是否安装成功,如果一切配置正确,浏览器应该能够安全地连接到您的Tomcat服务器,并且地址栏中会显示一个绿色的锁图标。

五、常见问题与解答

Q1: 如何在CentOS系统上生成自签名SSL证书?

A1: 在CentOS系统上生成自签名SSL证书的步骤如下:

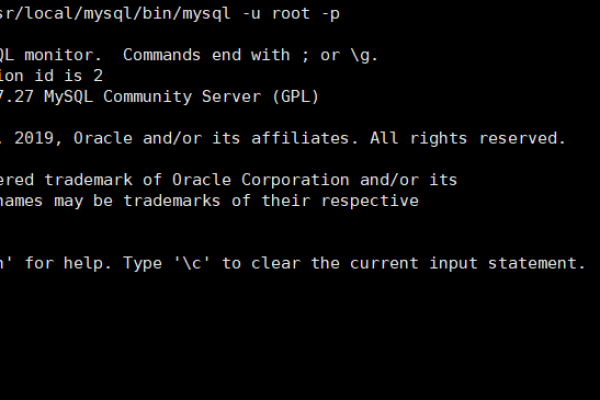

1、确保OpenSSL已安装:yum install openssl -y。

2、生成带密码的私有密钥:openssl genrsa -des3 -out server.key -rand 0x1000000000000000000。

3、移除密码保护(可选):openssl rsa -in server.key -out server-nopass.key。

4、生成自签名证书:openssl req -new -x509 -key server-nopass.key -out server.crt -days 3650。

5、生成PFX格式证书(可选):openssl pkcs12 -export -out server.pfx -in server.crt -inkey server-nopass.key。

6、转换PFX证书为PEM格式(可选):cat server.crt server-nopass.key > server.pem。

Q2: 如何更改Tomcat默认监听端口数?

A2: 要更改Tomcat默认监听的端口数,可以按照以下步骤操作:

1、打开Tomcat的server.xml配置文件。

2、找到<Server port="8005" shutdown="SHUTDOWN"标签,将port属性的值更改为您想要的端口号。

3、保存并关闭配置文件。

4、重新启动Tomcat服务以使更改生效。

通过以上步骤,您可以在CentOS系统上成功配置SSL证书,并确保Tomcat服务器的数据传输安全性,如果在配置过程中遇到任何问题,建议查阅相关文档或寻求专业技术支持。

各位小伙伴们,我刚刚为大家分享了有关“centos ssl 证书”的知识,希望对你们有所帮助。如果您还有其他相关问题需要解决,欢迎随时提出哦!