VHDL语言在数字电路设计中有哪些独特优势?

- 行业动态

- 2024-11-14

- 1

VHDL(VHSIC Hardware Description Language)是一种用于描述数字电路和系统的语言,它支持硬件的行为、结构和数据流的建模。

VHDL(Very-High-Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)是一种用于电子设计自动化的硬件描述语言,适用于描述逻辑门、触发器、时序电路等数字系统,以下是对VHDL语言的详细介绍:

VHDL基础语法结构

1、实体(Entity):实体是VHDL的最基本单位,定义了外部接口,可以认为是电路模块的“头文件”,它描述了设计的输入和输出信号。

entity example_entity is

port (

input_signal : in std_logic; -输入信号

output_signal : out std_logic -输出信号

);

end entity example_entity;2、架构(Architecture):架构描述了实体的行为或结构,可以看作是实体的“实现文件”,它包含了组件实例化、信号声明、过程语句等。

architecture behavior of example_entity is

begin

-逻辑描述

output_signal <= not input_signal;

end architecture behavior;3、信号(Signal)和变量(Variable):在VHDL中,信号用于描述设计中的数据传输,而变量通常用于描述局部的数据存储,信号和变量的作用在于描述设计中的数据流动和数据处理。

4、过程(Process):过程描述了设计中的行为和逻辑,可以包括对信号和变量的操作、时序逻辑的描述等。

VHDL数据类型与运算符

1、标量数据类型:包括位(bit)、布尔(boolean)、整数(integer)、自然(natural)和自然数(positive)。

bit:最基本的标量类型,有两个可能的值:’0’和’1’。

boolean:用于逻辑值,有两个可能的值:true和false。

integer:表示整数值,范围从$-2^{31}$到$2^{31}-1$。

natural:integer的一个子类型,只能表示非负整数。

positive:也是integer的一个子类型,表示正整数。

2、复合数据类型:包括数组(array)和记录(record)。

array:由相同类型的元素组成的集合,可以是一维或多维,std_logic_vector是一个常见的数组类型,用于表示一系列的std_logic值。

record:由不同类型的元素组成的结构体,每个元素都有自己的名字,这允许将相关数据捆绑在一起形成一个复杂的数据结构。

3、运算符:包括算术运算符(如加、减、乘、除)、逻辑运算符(如与、或、非)和关系运算符。

VHDL设计与仿真

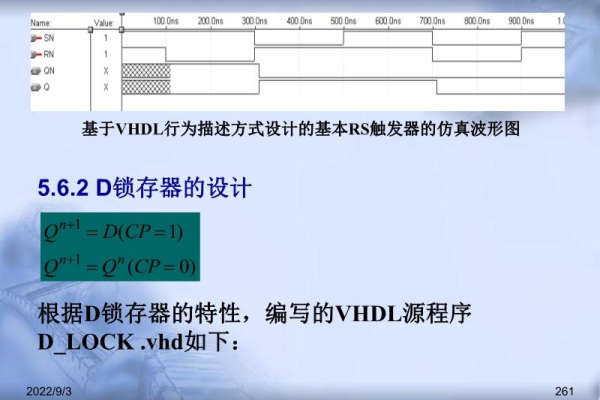

VHDL主要用于描述数字系统的结构、行为、功能和接口,它将一个设计分为外部(可视部分、端口)和内部(不可视部分、内部功能、算法)两部分,通过EDA工具,可以对VHDL源代码进行早期功能仿真,有利于大系统的设计与验证。

VHDL与其他硬件描述语言的比较

与Verilog相比,VHDL具有较强的系统级抽象描述能力,更适合行为级和RTL级的描述,而Verilog在门级开关电路描述方面较强,VHDL已成为IEEE标准所规范的硬件描述语言,得到了众多EDA公司的支持。

常见问题解答(FAQs)

Q1: VHDL与C、C++等高级编程语言有何不同?

A1: VHDL主要用于描述数字电路的结构和行为,其语法和描述风格类似于高级编程语言,但包含许多具有硬件特征的语句,与C、C++等语言不同,VHDL更侧重于硬件设计和并行处理,而不是软件编程的顺序执行。

Q2: VHDL在数字系统设计中的优势是什么?

A2: VHDL具有强大的语言结构,系统硬件抽象描述能力强、设计效率高;易于修改和发现错误;具有丰富的仿真语句和库函数,可进行早期行为仿真;设计与硬件电路关系不大,不依赖于器件,与工艺无关;移植性好;符合TOP-DOWN和CE设计思想;设计效率高,产品上市时间快,成本低;易于ASIC实现。

以上内容就是解答有关“vhdl语言”的详细内容了,我相信这篇文章可以为您解决一些疑惑,有任何问题欢迎留言反馈,谢谢阅读。

本站发布或转载的文章及图片均来自网络,其原创性以及文中表达的观点和判断不代表本站,有问题联系侵删!

本文链接:http://www.xixizhuji.com/fuzhu/23963.html