如何移除DedeCMS添加图片时自动添加的织梦水印?

- 行业动态

- 2024-09-05

- 8

在数字媒体管理平台DedeCMS(织梦)中,添加图片时经常会发现系统自动为图片加上了“织梦”的水印,对于希望去除这个水印的用户来说,了解如何操作以去掉这个默认设置变得非常重要,下面将详细指导您通过修改系统设置、文件调整等方法来去除图片上传时自动添加的水印:

1、修改后台系统设置:登录到织梦管理界面后,导航至“系统 > 系统基本参数 > 附件设置”,在该页面中取消勾选“图集是否使用水印(小图也会受影响)”选项,这是最直观的方法之一,通过关闭这一选项,可以阻止系统在上传的图片上自动添加水印。

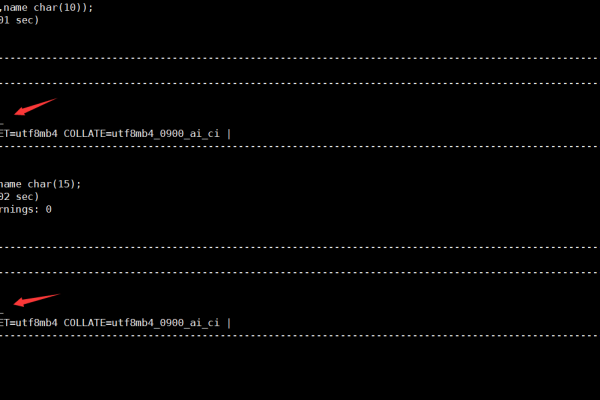

2、更改水印应用条件:如果您想要对特定尺寸或类型的图片不应用水印,可以通过修改配置文件实现,在dede/archives_do.php中找到相关上传代码,并将其中的参数调整为仅在满足特定条件时才添加水印,这种方法提供了更多的自定义空间,允许用户根据实际需要设定水印的应用规则。

3、替换系统默认的水印图片:如果您不希望完全去除水印,而是想更换为自定义的水印,可以通过上传新的水印图片并替换掉系统默认的水印图片来实现,具体步骤包括在后台上传新的水印图片,然后通过系统找到并替换掉默认的水印图片路径,这样,当系统自动添加水印时,便会使用您自定义的水印图片。

4、修改水印添加的相关代码:对于有一定编程基础的用户,可以直接修改处理水印的PHP文件,编辑dede/swfupload.php和include/helpers/upload.helper.php等文件,在这些文件中修改涉及水印添加的部分,从而实现去除或自定义水印的目的,这种方法要求用户具备一定的技术知识,但同时也提供了更高的自由度。

5、直接关闭上传图片加水印功能:另一个简单直接的方法是在后台的“图片水印设置”中,直接关闭“上传图片加水印”的功能,这样做虽然不能提供更多自定义选项,但却是最快且最彻底的解决方案,尤其适合那些不希望图片有任何水印的用户。

结合上述分析和操作步骤,为您提供更深入的指导和信息,以确保您能够顺利去除DedeCMS系统中上传图片时的默认水印:

注意备份: 在进行任何文件修改前,建议先进行文件备份,这可以防止在修改过程中发生错误导致的系统不稳定或数据丢失。

考虑影响: 去除水印可能会影响网站内容的版权保护,确保此举符合您的实际需求和法律要求。

适应更新: DedeCMS可能会不定期更新,记得检查每次更新后是否需要重新进行上述设置。

去除DedeCMS中添加图片时的水印是一个相对直接的过程,可以通过修改后台设置、替换水印图片或直接编辑系统文件来实现,根据您的具体需求选择合适的方法,并确保在进行任何修改前都进行了充分的备份准备,通过这些步骤,您可以轻松控制您的媒体内容,使之不受默认水印的影响。

FAQs

问:我修改了设置后还是自动添加了水印,怎么办?

答:请确认您已正确保存了所有修改,并清除了浏览器缓存或系统缓存,如果问题依旧,检查是否其他相关设置或插件影响了水印功能的正常工作。

问:我是否可以为特定的内容类型禁用水印?

答:是的,通过修改相关文件如 archives_do.php 和 upload.helper.php 中的代码,您可以自定义水印的添加条件,例如针对特定内容类型或图片大小不加水印。