MySQL排序技巧,如何优化你的查询排序效率?

- 行业动态

- 2024-10-05

- 4208

MySQL 排序(ORDER BY)

MySQL 中的ORDER BY 子句用于对查询结果进行排序,您可以使用它来根据一列或多列对结果进行升序(ASC)或降序(DESC)排序。

基本语法

SELECT column1, column2, ... FROM table_name ORDER BY column1 [ASC|DESC], column2 [ASC|DESC], ...;

column1, column2, ...:需要排序的列名。

ASC:升序排序(默认)。

DESC:降序排序。

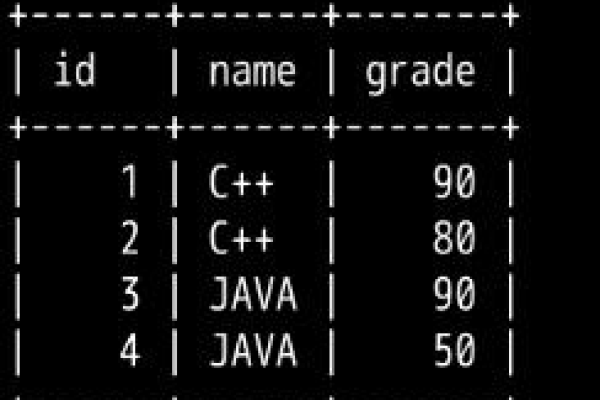

示例

以下是一个简单的示例,展示如何根据单列进行排序:

SELECT * FROM employees ORDER BY salary DESC;

这个查询将返回employees 表中所有记录,并按salary 列降序排列。

多列排序

如果您需要根据多个列进行排序,可以在ORDER BY 子句中指定多个列:

SELECT * FROM employees ORDER BY salary DESC, name ASC;

这个查询将首先按salary 列降序排列,如果salary 相同,则按name 列升序排列。

排序示例

以下是一些更复杂的排序示例:

1、升序排序:

SELECT * FROM products ORDER BY price ASC;

2、降序排序:

SELECT * FROM products ORDER BY price DESC;

3、多列升序排序:

SELECT * FROM orders ORDER BY order_date ASC, total_amount ASC;

4、多列降序排序:

SELECT * FROM orders ORDER BY order_date DESC, total_amount DESC;

5、混合排序:

SELECT * FROM customers ORDER BY last_name DESC, first_name ASC;

在这个查询中,如果last_name 相同,则按first_name 升序排列。

注意事项

如果没有指定排序顺序,则默认为升序。

如果需要按照非列名进行排序(根据字符串的字典顺序),可以使用ORDER BY 子句中的表达式或函数。

ORDER BY 子句可以与LIMIT 子句结合使用,以限制结果集的大小。

希望这些信息能够帮助您更好地理解和使用 MySQL 中的排序功能。

本站发布或转载的文章及图片均来自网络,其原创性以及文中表达的观点和判断不代表本站,有问题联系侵删!

本文链接:http://www.xixizhuji.com/fuzhu/21298.html