CPU如何利用信号访问存储器?

- 行业动态

- 2025-01-16

- 3183

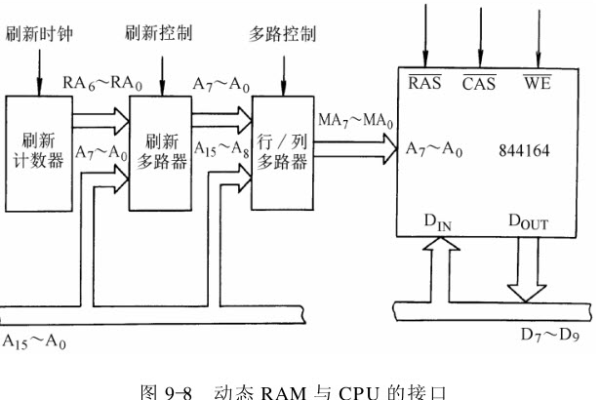

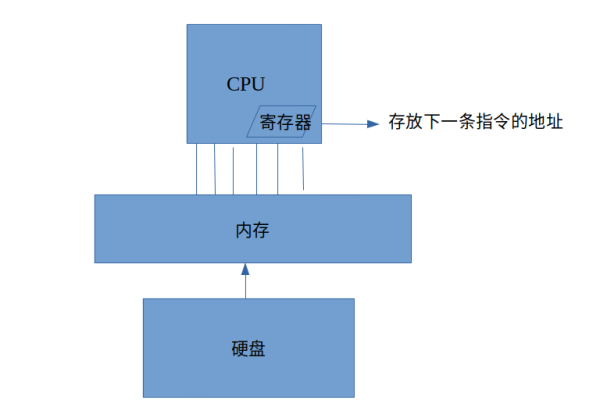

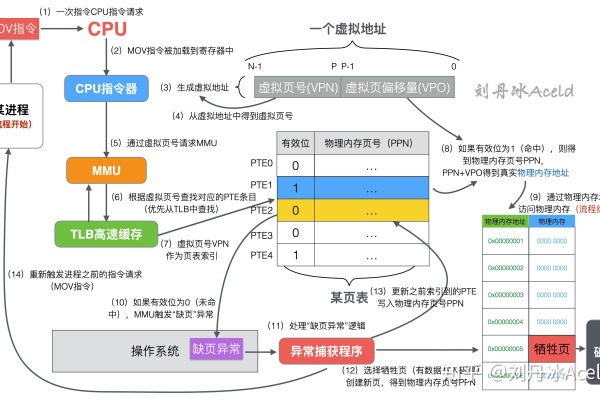

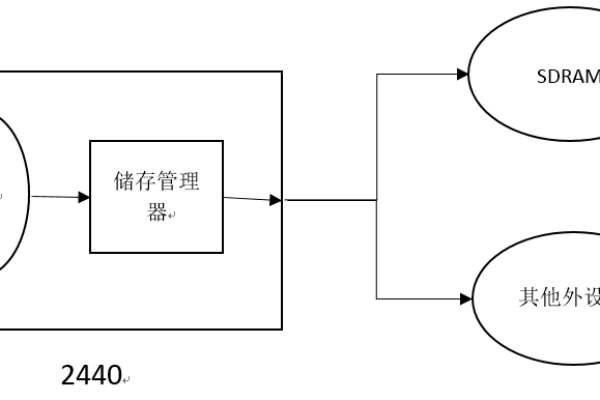

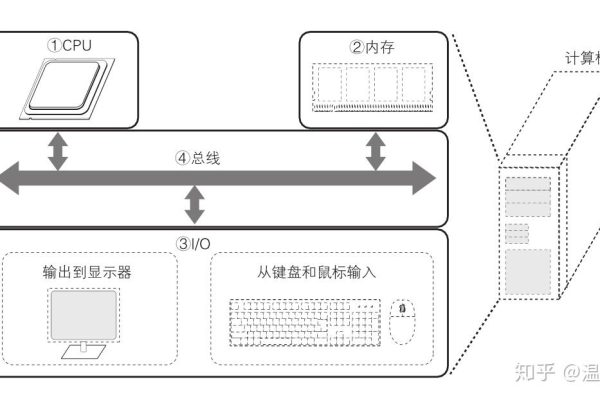

在计算机系统中,CPU(中央处理单元)与存储器之间的通信是通过一系列特定的信号实现的,这些信号主要分为三类:地址总线、数据总线和控制总线,以下是详细解释:

一、地址总线(Address Bus)

地址总线用于传送存储单元的地址信息,CPU通过地址总线将需要访问的存储单元的地址发送到存储器,以便存储器能够定位并选择相应的存储单元进行读写操作,8086/8088 CPU的地址总线为20位,其寻址范围为1MB。

二、数据总线(Data Bus)

数据总线用于传送数据信息,当CPU需要从存储器读取数据时,数据会通过数据总线从存储器传输到CPU;反之,当CPU需要向存储器写入数据时,数据会通过数据总线从CPU传输到存储器,数据总线的宽度决定了一次能够传输的数据位数,例如8086/8088 CPU的数据总线为16位。

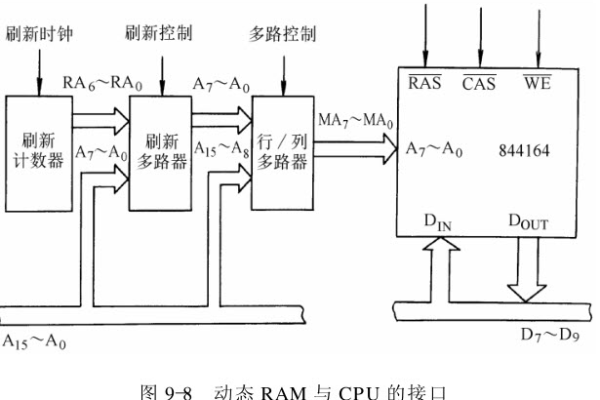

三、控制总线(Control Bus)

控制总线用于传送各种控制信号,以协调CPU与存储器之间的通信,这些控制信号包括读/写信号、时钟信号、同步信号等,8086/8088 CPU的控制信号包括ALE(地址锁存允许)、DEN(数据允许)、DT/R(数据收发)、M/IO(存储器/输入输出控制)、WR(写信号)、RD(读信号)等。

四、具体信号及其作用

1、ALE(Address Latch Enable):地址锁存允许信号,当ALE信号有效时,CPU将地址信息发送到地址总线上,以便存储器能够锁存这个地址。

2、DEN(Data Enable):数据允许信号,当DEN信号有效时,数据总线上的数据可以传输。

3、DT/R(Data Transmit/Receive):数据收发信号,用于指示数据是传输还是接收。

4、M/IO(Memory/Input Output):存储器/输入输出控制信号,用于区分当前操作的是存储器还是I/O设备。

5、WR(Write):写信号,当WR信号有效时,表示CPU正在向存储器写入数据。

6、RD(Read):读信号,当RD信号有效时,表示CPU正在从存储器读取数据。

7、HOLD:当外部设备请求使用总线时,会发出HOLD信号,如果CPU响应此请求,则会释放总线控制权。

8、HLDA:HOLD响应信号,当CPU响应HOLD请求时,会发出HLDA信号,表示总线已被外部设备占用。

9、INTR:中断请求信号,当外部设备需要中断CPU的当前操作时,会发出INTR信号。

10、INTA:中断响应信号,当CPU响应中断请求时,会发出INTA信号。

11、READY:准备好信号,用于指示存储器或I/O设备是否准备好进行数据传输。

12、RESET:复位信号,用于初始化CPU的状态。

五、相关FAQs

Q1: CPU访问存储器时,哪些信号必须同时有效?

A1: CPU访问存储器时,必须同时有效的信号包括地址锁存允许信号(ALE)、数据允许信号(DEN)、以及读/写控制信号(RD/WR),这些信号确保了正确的地址和数据能够在适当的时间被锁定和传输。

Q2: 当外部设备请求使用总线时,CPU如何响应?

A2: 当外部设备请求使用总线时,会发出HOLD信号,如果CPU响应此请求,它会释放总线控制权,并通过发出HLDA信号来确认总线已被外部设备占用,CPU会使地址/数据总线和控制状态线置高阻,以避免干扰外部设备的数据传输。

小编有话说

CPU访问存储器的过程是一个复杂而精密的操作,涉及多个信号的协同工作,了解这些信号的作用和工作原理,对于深入理解计算机系统的运行机制至关重要,希望本文能够帮助读者更好地理解CPU与存储器之间的通信过程,并在实际应用中有所启发。

本站发布或转载的文章及图片均来自网络,其原创性以及文中表达的观点和判断不代表本站,有问题联系侵删!

本文链接:http://www.xixizhuji.com/fuzhu/1964.html