CPU真的能直接访问存储器吗?

- 行业动态

- 2025-01-19

- 4

CPU能否访问存储器

在现代计算机系统中,CPU(中央处理器)与存储器之间的关系至关重要,CPU通过多种方式访问存储器,以实现数据的读取和写入操作,以下将详细解释CPU如何访问存储器,包括逻辑地址到物理地址的转换、虚实地址、TLB(快表)、Cache(缓存)等技术的应用。

一、CPU访问存储器的整体流程

CPU访问存储器的过程通常分为几个步骤:提供逻辑地址、虚实地址转换、访存次数、虚实转换地址“变化”、虚存大小、虚存&Cache区别、TLB(Translation Lookaside Buffer)、段页式存储管理等。

1、提供逻辑地址:程序员交给CPU的是逻辑地址,要进行虚实地址转换才能找到该虚拟地址所对应的数据实际存放的位置。

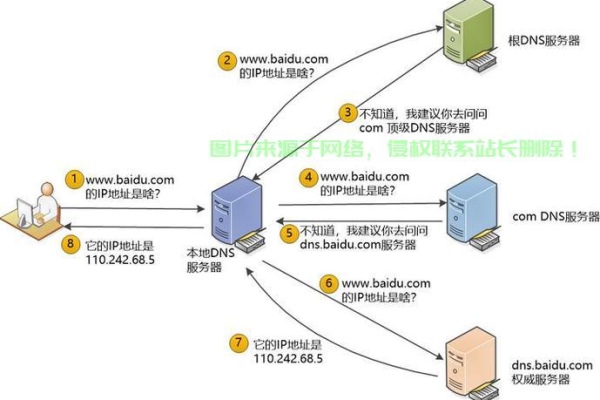

2、虚实地址转换:虚页号与实页号的对应关系存在页表(Page Table)中,活跃的页表项存在TLB中,如果TLB不命中,再查页表,若页表还不命中,说明该页面还未调入主存,需发出缺页中断,从辅存中调入并更新页表和TLB。

3、访存次数:指令过程——取数、运算&写回,取数读取xaddr可能不需要访存(直接访问Cache),而写直通法需要把数据同时写入Cache和主存。

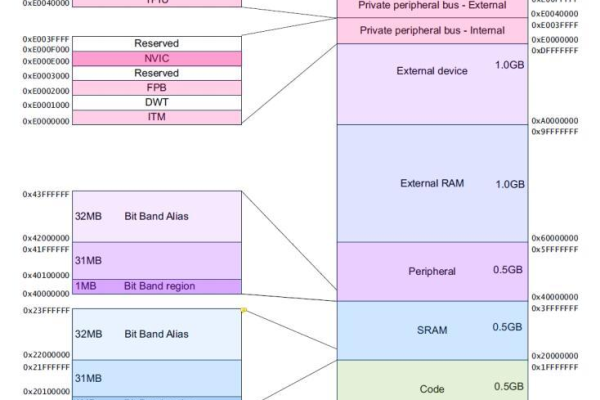

4、虚实转换地址“变化”:当主存地址和Cache地址采用直接映射方式时,地址映射表的大小由主存块号和Cache组数决定。

5、虚存大小:虚存容量由CPU的寻址范围决定,通常小于或等于内存+外存容量的总和。

6、虚存&Cache区别:虚存是解决容量问题,通过时间换空间;Cache是解决速度问题,通过金钱换时间。

7、TLB:高速存储器(SRAM)组成,按查找内容访问(查找速度快依赖于硬件本身,而非搜索算法)。

8、段页式存储管理:首先访问内存中的段表,然后访问内存中的页表,最后访问指令/数据所在的内存页面。

二、地址结构与虚实地址转换

1、虚实地址:虚拟地址分为虚页号和页内地址;物理地址分为实页号和页内地址。

2、Cache-主存地址映射:Cache-主存体系中,地址先分为块号和块内地址,对应不同的映射方式,主存地址的块号需要拆分成不同的字段,高位均为标记字段,需要存入Cache。

| 主存字块标记 | 组地址 | 字块内地址 |

3、页表寄存器PTR:页号P和页表长度M比较康康是否越界,若没越界才根据页号和块号找到对应的页表项。

4、界地址寄存器:比较逻辑地址的值和寄存器的值判断是否越界。

5、重定位寄存器:逻辑地址+寄存器的值=物理地址。

三、Cache与主存之间的交互

1、Cache的作用:高速缓冲存储器位于主存和CPU之间,用来存放正在执行的程序段和数据,以便CPU能高速地使用它们,其存取速度可与CPU的速度相匹配,但存储容量小、价格高。

2、Cache的工作原理:利用程序访问的局部性原理,把程序中正在使用的部分存放在Cache中,使CPU的访存操作大多针对Cache进行,从而大大提高程序的执行速度。

3、Cache的替换策略:常见的替换算法包括随机(RAND)算法、先进先出(FIFO)算法、近期最少使用(LRU)算法和最不经常使用(LFU)算法。

4、Cache的写策略:包括写直达法、写回法等,写直达法在数据写入Cache的同时也会写入主存,而写回法则在数据被替换时才写回主存。

四、提高CPU访问存储器效率的技术

为了提高CPU访问存储器的速度和效率,计算机系统采用了多种技术,如存储器缓存、存储器交错、存储器通道等,这些技术可以减少CPU与存储器之间的数据传输次数,从而提高系统的性能和效率。

1、存储器缓存:用于临时存储常用数据和指令,以便CPU快速访问。

2、存储器交错:通过并行访问多个存储器模块来提高数据传输速率。

3、存储器通道:增加存储器总线的宽度或速度,以提高数据传输速率。

CPU能够通过多种方式访问存储器,并通过一系列优化技术提高访问速度和效率,这些技术和方法共同构成了现代计算机系统的基础,使得CPU能够高效地处理各种复杂的计算任务。