cpu与存储器的连接视频

- 行业动态

- 2025-02-12

- 4473

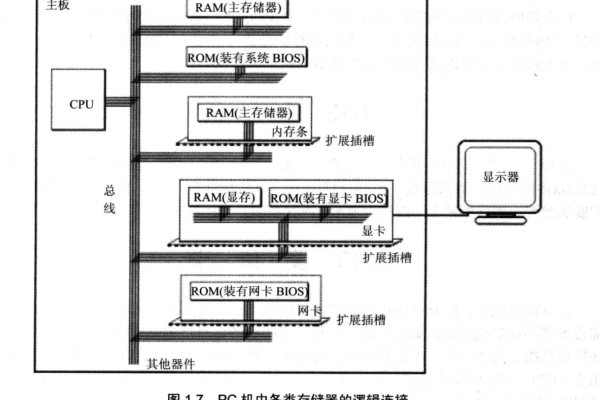

连接方式

地址总线连接:

CPU通过地址总线向存储器发送地址信息,以确定寻址的存储单元的端口地址,地址总线的位数决定了可寻址的范围。

数据总线连接:

CPU通过数据总线与存储器进行数据传输,数据总线的宽度决定了每次传输数据的位数,例如8位、16位、32位或64位等。

控制总线连接:

包括读写控制信号、片选信号等,读写控制信号用于指定数据传输的方向,即CPU从存储器读取数据或向存储器写入数据,片选信号则用于选择特定的存储器芯片或I/O设备,确保数据的正确传输。

译码方法

全译码法:

将地址总线中除片内地址以外的全部高位地址接到译码器输入端参与译码,每个存储单元的地址是唯一的,不存在地址重叠,但连接电路复杂。

部分译码法:

只将高位地址线的一部分进行译码,由于高位地址线与存储器地址无关,所以存在地址重叠问题,选用不同的高位地址线,对应的地址空间也不同。

线选法:

高位地址线不经过译码,直接作为存储器芯片的片选信号,高位地址用于选择芯片,低位地址线实现寻址,这种方法连接简单,但当采用线选时,高位地址未全部用完、而又没用对其实施控制时,会出现地址的不连续和多义性,且寻址空间变少。

存储器类型及特点

随机存取存储器(RAM):

静态RAM(SRAM):速度快,不需要刷新电路,但集成度低、功耗较大、成本高,常用于高速缓存等对速度要求较高的场合。

动态RAM(DRAM):需要定期刷新以保持数据,集成度高、成本低、功耗小,广泛应用于计算机的主内存。

只读存储器(ROM):

只能读出而不能写入,常用于存储固定的程序和数据,如BIOS等,具有非易失性,即使断电也能保持数据不丢失。

闪存:

一种非易失性的存储器,结合了RAM的访问速度和ROM的非易失性特性,常用于固态硬盘、U盘等存储设备。

连接示例

以一个具有16根地址线、8根数据线的CPU,以及1Kx4位RAM、4Kx8位RAM、8Kx8位RAM、2Kx8位ROM、4Kx8位ROM、8Kx8位ROM等存储芯片为例,假设主存地址空间分配为6000H ~ 67FFH为系统程序区,6800H ~ 6BFFH为用户程序区,可使用74138译码器进行片选,具体连接步骤如下:

系统程序区:

使用ROM,根据地址范围6000H ~ 67FFH,确定A0~A10变化,同时CPU为8根数据线,所以选用2K×8位的ROM。

将A13、A12、A11分别连接74138译码器的C、B、A端,如果为1 0 0,Y4有效,选中该ROM。

G1高电平有效,连接A14;G2B可以连接在74138译码器的G2A上(低电平有效),MREQ低电平时,才访问存储器,正好可以连接G2B。

用户程序区:

使用RAM,根据地址范围6800H ~ 6BFFH,确定A0~A9变化,为1K×8位,题目没有提供这样的芯片,可以用2片1K×4位芯片,通过位扩展变成1K×8位芯片。

Y5和A10通过与门输出,作为片选线连接两个RAM,两个RAM因为要位扩展,所以CPU数据线各连接4条。

CPU与存储器的连接是一个复杂而精细的过程,涉及多个方面的考量和设计,通过合理的连接方式、译码方法和存储器类型的选择,可以实现高效、稳定的数据存储和访问。

本站发布或转载的文章及图片均来自网络,其原创性以及文中表达的观点和判断不代表本站,有问题联系侵删!

本文链接:https://www.xixizhuji.com/fuzhu/112189.html